## CUSTOM INTEGRATED AMPLIFIER CHIP FOR VLF MAGNETIC RECEIVER

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> Sarah Katharine Harriman August 2010

## Abstract

Electronic systems for collecting measurements in harsh, remote environments face special challenges that often require custom designs. These systems must have the power capacity, data storage, and robustness to record high fidelity data for many months with no human contact. In this work, an integrated preamplifier for a magnetic sensor is designed to satisfy the size, weight, power, temperature, and noise specifications for long term deployment in Antarctica. The low impedance magnetic antenna (1  $\Omega$ -1 mH) requires a low input impedance amplifier and operates in the VLF (Very Low Frequency) range (50 Hz–30 kHz). At these low frequencies, 1/f noise becomes the dominating issue that limits performance. Due to the higher 1/f noise corner of MOSFET devices, only bipolar-junction transistors (BJTs) must be used in noise-critical parts of the design. Because of recent interest in BJTs for their superior performance at high frequencies in the gigahertz range, they are becoming available in the fabrication processes for integrated chips. With these new opportunities for using BJTs in integrated designs, low frequency amplifiers used in low noise applications can be integrated for the first time. In this thesis, a low impedance custom amplifier is presented that was implemented in National Semiconductor Corporation's BiCMOS process which meets the impedance and temperature requirements while achieving 2 pA/ $\sqrt{\text{Hz}}$  current noise in band with only 5 mW of power. This noise level corresponds to a magnetic field noise of 0.25 fT/ $\sqrt{\text{Hz}}$  for the loop antenna that is used for this application. The amplifier is field tested at the South Pole, successfully collecting data suitable for science research.

## Acknowledgements

This project would not have been successful without the contributions from many people. First, my advisor Umran Inan guided this project from the beginning, including initiating the project idea and gathering support. His level of dedication to his work and his commitment to the success of his students he shows is quite rare. Ivan Linscott provided the technical advising and many extremely helpful discussions. It is always a pleasure to discuss ideas with such a creative person. John Pauly kindly agreed to join my committee on short notice and lend his expertise in the completion of this dissertation.

This work was made possible by the collaboration with National Semiconductor, in particular, Dr. Ahmed Bahai and Bijoy Chatterjee. National Semiconductor graciously extended access to their model and process information for our design work, answered our many questions, and fabricated the completed design. The initial portion of this work was supported by a CIS Seed Grant, and then the work was completed under several grants from the National Science Foundation's Office for Polar Research (grants 0341165, 0636927, and 0840058).

Many thanks are due to Dr. Evans Paschal as well for the enlightening technical discussions. His competence of analog design and easy, clear explanations of complex concepts make him invaluable within our research group as well as this research field.

The VLF group as a whole is enthusiastic, dedicated, and a pleasure to work with. I continue to be impressed with the fact that everyone works together so well, and such collaborations result in much greater success than what could be achieved by any of us working alone. I will miss the friendly, team-spirited environment. Special thanks belongs to Jeff Chang who is not only is technically an expert in all the hardware projects in the group, but who is also always ready to help. I learned so much from the collaborations with Ben Mossawir, and it is so helpful to have another analog designer to discuss issues with. Charles Wang spent many hours keeping the Cadence simulation software and computer running in addition to his own thesis work. Max Klein designed and built the digital electronics and mechanical enclosures for the project. The field test would not have been possible without his work. Shaolan Min and Helen Niu do so much behind the scenes to keep everything running smoothly, it often seems like they do magic.

My parents deserve thanks for the great start they gave me both personally and academically. They provided the foundation of my work and their unwavering support is deeply appreciated. My husband was my greatest friend through this process, and contributed in a variety of ways, from computer issues, to technical discussions, to editing assistance. I am so fortunate to have found such a wonderful life companion.

# Contents

| $\mathbf{A}$ | bstra | nct                                       | v  |

|--------------|-------|-------------------------------------------|----|

| A            | cknov | wledgements                               | vi |

| 1            | Intr  | roduction                                 | 1  |

|              | 1.1   | Project Overview                          | 1  |

|              | 1.2   | Magnetic Receiver System Redesign Goals   | 2  |

|              | 1.3   | Previous Magnetic Sensors                 | 3  |

|              |       | 1.3.1 Magnetic Sensors in Neural Research | 4  |

|              |       | 1.3.2 SQUIDs                              | 4  |

|              |       | 1.3.3 Low Frequency Magnetometers         | 5  |

|              | 1.4   | Analog Front End Overview                 | 6  |

|              |       | 1.4.1 Amplifier Specifications            | 7  |

|              | 1.5   | Contributions                             | 7  |

|              | 1.6   | Dissertation Organization                 | 8  |

| <b>2</b>     | Bac   | kground                                   | 9  |

|              | 2.1   | Antenna Design                            | 9  |

|              |       | 2.1.1 Antenna Sensitivity                 | 10 |

|              | 2.2   | Transformer                               | 13 |

|              |       | 2.2.1 Transformer Frequency Response      | 14 |

|              |       | 2.2.2 Transformer Effects on System Noise | 15 |

|              | 2.3   | Antenna and Transformer Parameters        | 17 |

|              |       | 2.3.1 Antenna Parameters                  | 17 |

|   |                   | 2.3.2   | Transformer Parameters                                                                                                          |  |  |

|---|-------------------|---------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

|   | 2.4 Noise Sources |         |                                                                                                                                 |  |  |

|   |                   | 2.4.1   | Thermal Noise                                                                                                                   |  |  |

|   |                   | 2.4.2   | Shot Noise                                                                                                                      |  |  |

|   |                   | 2.4.3   | Flicker Noise                                                                                                                   |  |  |

|   |                   | 2.4.4   | Input Referred Noise of An Amplifier                                                                                            |  |  |

|   |                   | 2.4.5   | Noise in Multiple Stages                                                                                                        |  |  |

|   | 2.5               | Transi  | istor Models                                                                                                                    |  |  |

|   |                   | 2.5.1   | Bipolar Transistor Characteristics                                                                                              |  |  |

|   |                   | 2.5.2   | Bipolar Transistor Noise Model                                                                                                  |  |  |

|   |                   | 2.5.3   | MOSFET Transistor Characteristics                                                                                               |  |  |

|   |                   | 2.5.4   | MOSFET Noise Model                                                                                                              |  |  |

| 3 | Inte              | egrated | d Amplifier Challenges 30                                                                                                       |  |  |

|   | 3.1               | Design  | n Requirements                                                                                                                  |  |  |

|   | 3.2               | Ampli   | fier Design Challenges                                                                                                          |  |  |

|   |                   | 3.2.1   | Bipolar Transistors Required                                                                                                    |  |  |

|   |                   | 3.2.2   | No PNP Transistors Available                                                                                                    |  |  |

|   |                   | 3.2.3   | Stages Must be DC Connected                                                                                                     |  |  |

|   |                   | 3.2.4   | Headroom $\ldots \ldots 33$                                      |  |  |

|   | 3.3               | Previo  | ous Work                                                                                                                        |  |  |

| 4 | Am                | plifier | Design 36                                                                                                                       |  |  |

|   | 4.1               | Ampli   | fier Overview                                                                                                                   |  |  |

|   | 4.2               | First S | Stage Topology and Design Relationships                                                                                         |  |  |

|   |                   | 4.2.1   | Topology                                                                                                                        |  |  |

|   |                   | 4.2.2   | First Stage Input Impedance                                                                                                     |  |  |

|   |                   | 4.2.3   | First Stage Gain                                                                                                                |  |  |

|   |                   | 4.2.4   | First Stage Frequency Response                                                                                                  |  |  |

|   |                   | 4.2.5   | First Stage Noise                                                                                                               |  |  |

|   |                   | 4.2.6   | $Temperature \dots \dots$ |  |  |

|   | 4.3               | Noise   | Optimization                                                                                                                    |  |  |

|   | 4.4  | First Stage Final Design                          | 51 |

|---|------|---------------------------------------------------|----|

|   | 4.5  | Second Stage                                      | 54 |

|   |      | 4.5.1 Second Stage Gain                           | 55 |

|   |      | 4.5.2 Second Stage Frequency Response             | 55 |

|   |      | 4.5.3 Second Stage Noise                          | 56 |

|   |      | 4.5.4 Second Stage Design                         | 56 |

|   | 4.6  | Output Stage                                      | 58 |

|   |      | 4.6.1 Third Stage Gain                            | 59 |

|   |      | 4.6.2 Third Stage Linearity                       | 60 |

|   | 4.7  | DC Level Control                                  | 61 |

|   | 4.8  | Full Amplifier                                    | 62 |

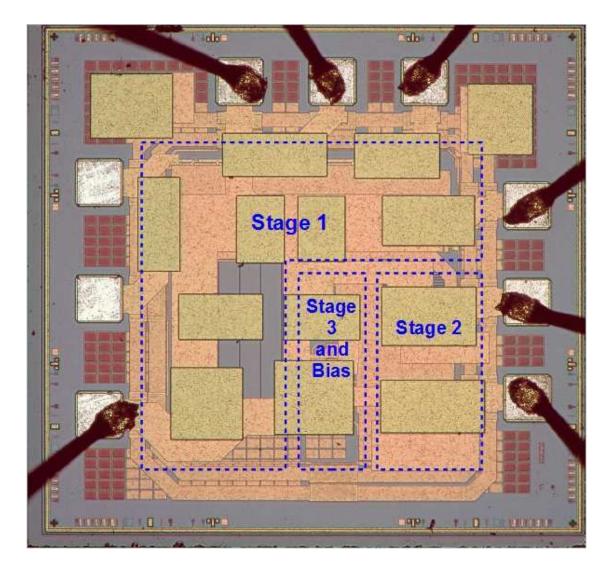

|   | 4.9  | Layout                                            | 64 |

| _ | -    |                                                   |    |

| 5 |      | ting Method                                       | 66 |

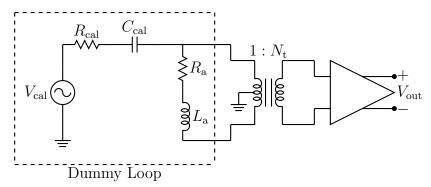

|   | 5.1  | Signal Injection                                  | 66 |

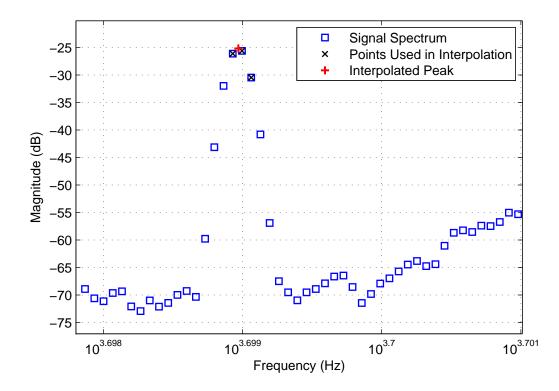

|   | 5.2  | Detecting Signals in the Presence of Strong Noise | 69 |

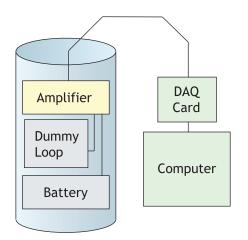

|   | 5.3  | End-to-End Test Setup                             | 72 |

| 6 | Mea  | asured Amplifier Performance                      | 74 |

|   | 6.1  | Power Consumption                                 | 74 |

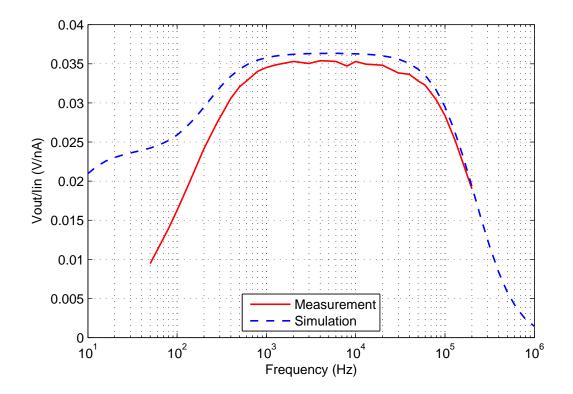

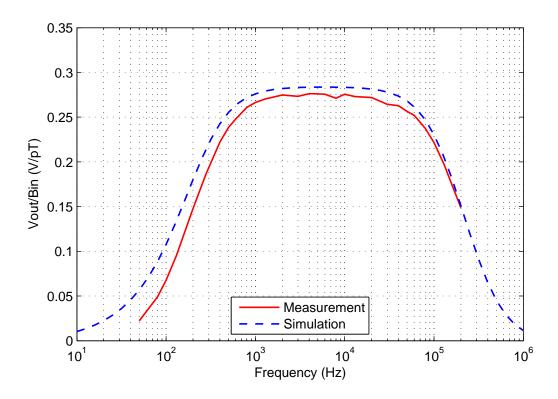

|   | 6.2  | Gain and Frequency Response                       | 74 |

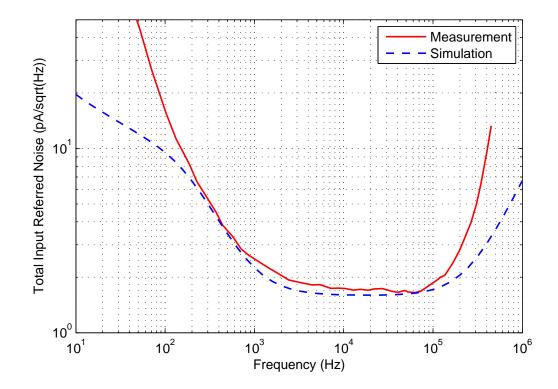

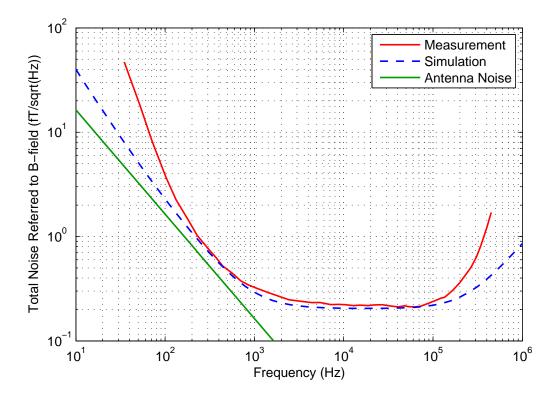

|   | 6.3  | Noise and Sensitivity                             | 76 |

|   | 6.4  | Linearity                                         | 78 |

| 7 | Syst | tem Design                                        | 80 |

|   | 7.1  | Preamplifier Board                                | 80 |

|   | 7.2  | Anti-Aliasing Filter                              | 82 |

|   | 7.3  | Field Test                                        | 86 |

| 8 | Disc | cussion                                           | 89 |

|   | 8.1  | Future Work                                       | 89 |

|   | 8.2  | Other Applications                                | 90 |

|   |      |                                                   |    |

Bibliography

92

# List of Tables

| 2.1 | Constants for Various Magnetic Loop Antenna Shapes                            | 11 |

|-----|-------------------------------------------------------------------------------|----|

| 2.2 | Magnetic Field Antenna Designs with 1 $\Omega – 1$ mH Impedance $\ . \ . \ .$ | 18 |

| 3.1 | Summary of Previously Published Work                                          | 35 |

# List of Figures

| 1.1  | Analog Block Diagram                                 | 6  |

|------|------------------------------------------------------|----|

| 2.1  | Analog Front End Models                              | 10 |

| 2.2  | Frequency Response of Antenna and Transformer        | 20 |

| 2.3  | Amplifier Noise Model Simplification                 | 23 |

| 2.4  | Noise Model of Multiple Stages                       | 24 |

| 2.5  | BJT Small Signal Model                               | 25 |

| 2.6  | BJT Noise Model                                      | 26 |

| 2.7  | MOSFET Small Signal Model                            | 28 |

| 2.8  | MOSFET Noise Model                                   | 28 |

| 4.1  | Block Diagram of Amplifier Chip                      | 37 |

| 4.2  | First Stage Topology                                 | 38 |

| 4.3  | High Frequency Model of First Stage                  | 42 |

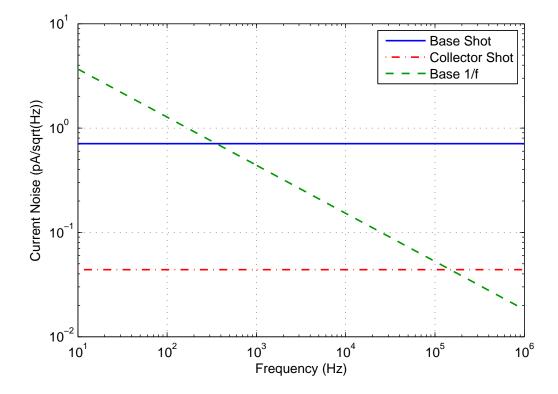

| 4.4  | Comparison of Noise Sources in an NPN BJT            | 43 |

| 4.5  | Noise Model of First Stage                           | 44 |

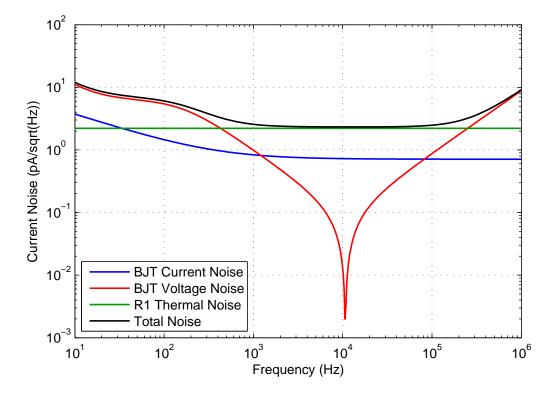

| 4.6  | Comparison of First Stage Noise Sources              | 46 |

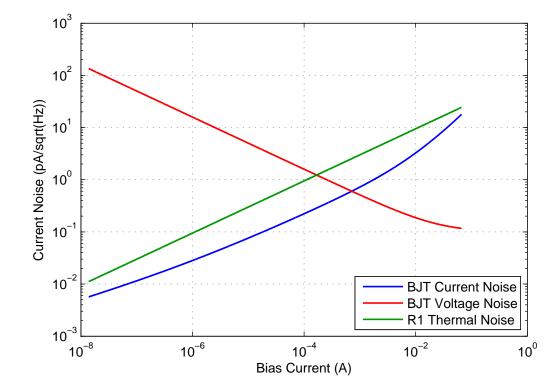

| 4.7  | First Stage Noise Components in Terms of $I_{\rm C}$ | 48 |

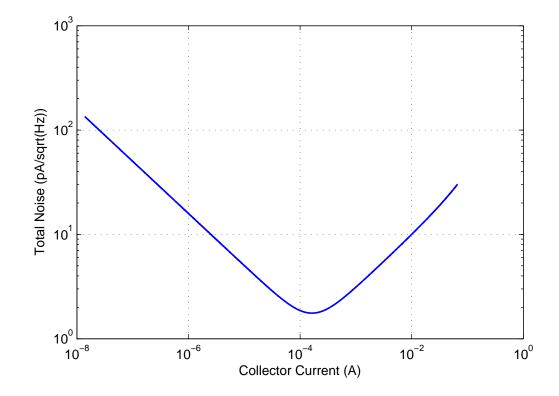

| 4.8  | Determination of Minimum First Stage Noise Current   | 49 |

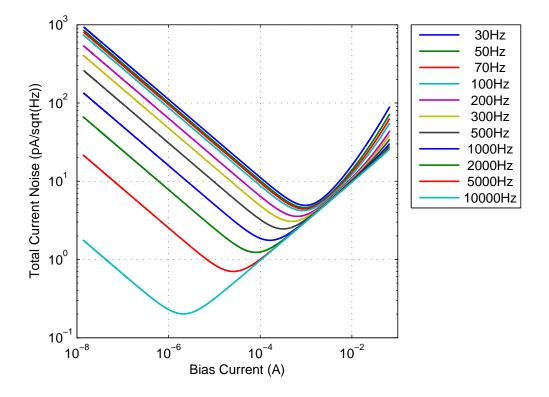

| 4.9  | First Stage Noise Current at Various Frequencies     | 50 |

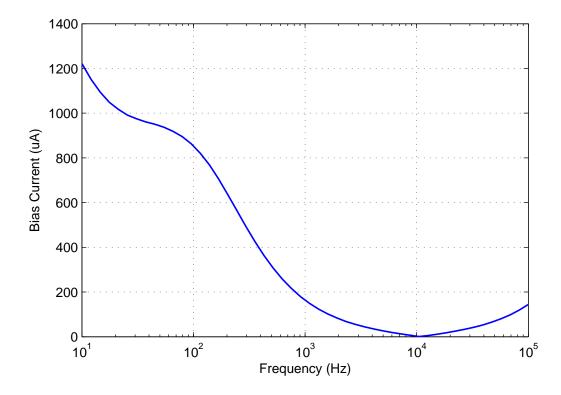

| 4.10 | Minimum First Stage Noise Currents Across Frequency  | 51 |

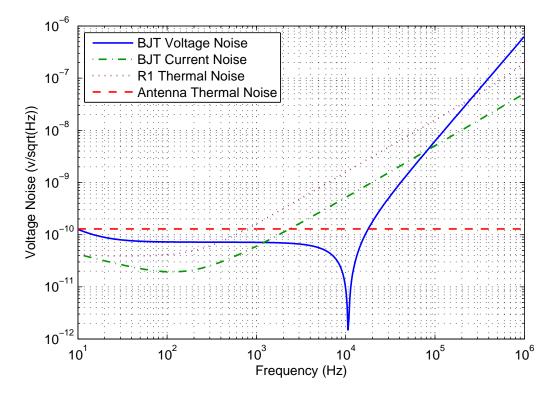

| 4.11 | First Stage Noise Referred to Antenna                | 52 |

| 4.12 | First Stage Noise Referred to Input Field            | 53 |

| 4.13 | Second Stage Topology                                | 54 |

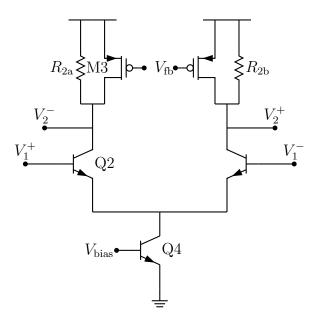

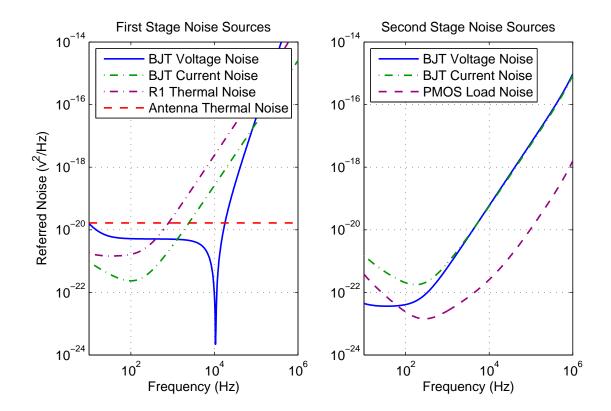

| 4.14 | Noise Components of First Two Stages                                   |

|------|------------------------------------------------------------------------|

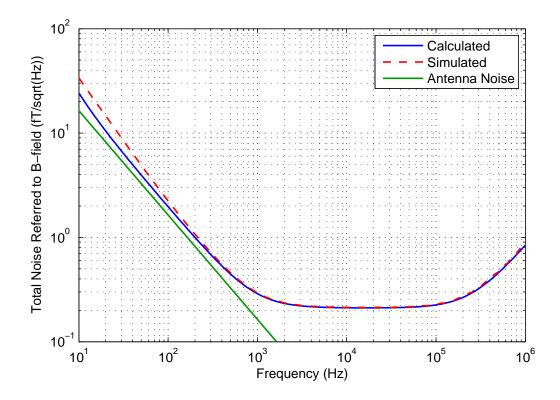

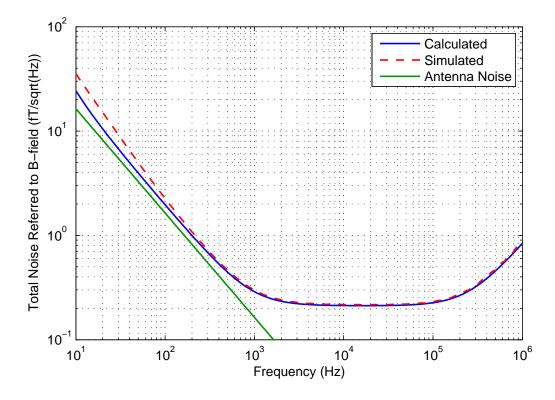

| 4.15 | Field Noise of First Two Stages    58                                  |

| 4.16 | Third Stage Topology                                                   |

| 4.17 | Schematic of DC Control                                                |

| 4.18 | Current Gain of Full Amplifier                                         |

| 4.19 | Current Noise of Full Amplifier                                        |

| 4.20 | Chip Die Photo                                                         |

| 5.1  | Schematic of Dummy Loop and Testing Configuration                      |

| 5.2  | Example of Interpolation For Determining Signal Magnitudes $\ldots$ 71 |

| 5.3  | Block Diagram of Testing Setup                                         |

| 6.1  | Measured Current Gain                                                  |

| 6.2  | Measured Field Gain                                                    |

| 6.3  | Measured Input Referred Current Noise                                  |

| 6.4  | Measured Sensitivity                                                   |

| 7.1  | Schematic of Preamp Board                                              |

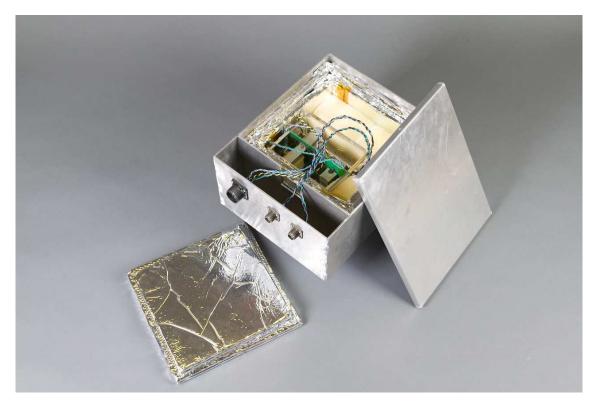

| 7.2  | Photo of Preamp Box                                                    |

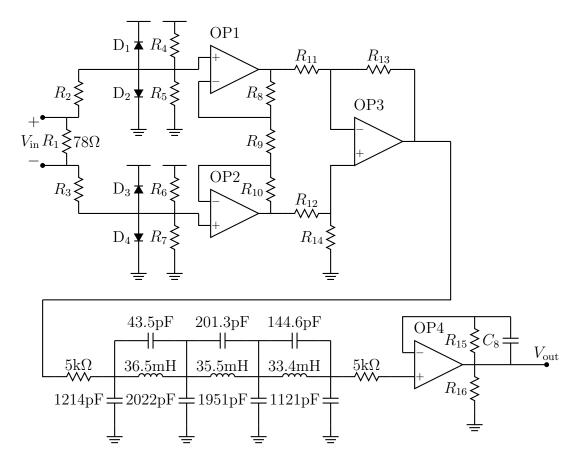

| 7.3  | Schematic of Filter Board                                              |

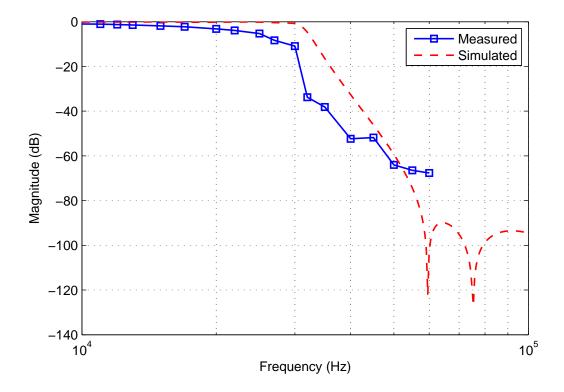

| 7.4  | Filter Response                                                        |

| 7.5  | Filter 3 dB Point                                                      |

| 7.6  | Photo of Digital Box                                                   |

| 7.7  | Example Data From Antarctica                                           |

## Chapter 1

## Introduction

## 1.1 **Project Overview**

Low frequency electromagnetic waves have long wavelengths and can travel far distances, both along the surface of the Earth and along the magnetic field lines up into the ionosphere. By observing these signals in the 50 Hz–30 kHz range, generated either by lightning or large transmitters, valuable information is obtained about lightning, the ionosphere, and the near-Earth space environment [40, 56]. Since there is so much manmade noise in this frequency range, and since shielding is difficult, the receivers used to detect these signals are often located in remote areas far from power lines, generators, and other electronics [32, 53]. One of the best locations of scientific interest is near the South Pole and other locations in Antarctica [18]. Since the mid-to-high latitude magnetic field lines of interest, and the electromagnetic waves that follow them, intercept the surface of the Earth near the South Pole, a receiver located there can detect signals generated in the Van Allen radiation belts [46, pp. 51-54], which is a region of near-Earth space of particular scientific interest.

For this dissertation, a magnetic receiver system was desired that is capable of detecting such signals in Antarctica by operating unattended for an entire year. Magnetic receivers are used to detect these waves instead of electric receivers because they have better noise performance at low frequencies. Also, they are less affected by nearby metallic structures and do not require a ground plane. The inhospitable environment and lack of power source make it difficult to build durable equipment that is also sensitive. Additionally, all travel is done by airplanes specially fitted for landing on snow, making it very expensive to service these remote sites to replenish the power supply renewal or for maintenance.

The receiver system designed and constructed during the course of this work replaces an older system used at several Antarctic sites which were deployed in the early 1990s, described in [41]. By reducing the cost of deployment and maintenance, many more sites can be added to the program to provide a clearer picture of the natural electromagnetic wave environment near the South Pole. Because of all of the technological advances over the past 20 years since the older system was developed, the new system required a complete redesign to incorporate the currently available parts, resulting in a much more compact, low power design.

### **1.2** Magnetic Receiver System Redesign Goals

The previous system (described in detail in [41]) uses about 7 W of power during operation, and one of the major expenses of the research program is flying the fuel to these sites. Therefore, the first major goal for the redesign effort is to reduce the power so that the whole system can last for a year on a single set of batteries. With sufficient data storage, the new system can operate for a full year with no maintenance. Additionally, no extra power is used to heat the electronics, and instead the system must survive the much colder temperatures.

Next, the electronics in the old system are stored in a small heated hut that is shared with other projects. These huts are very expensive to build because all of the parts have to be flown to the remote receiver site, and then it takes several days for the construction. The number of sites is limited to only seven, but with a smaller receiver that could be deployed more quickly, the number of sites could be greatly expanded. Therefore, the second main goal of the system redesign is to reduce physical size so that each system can be deployed within several hours, and require only a single airplane trip. The temperature in Antarctica varies widely, and can swing from  $-15^{\circ}$ C to  $-80^{\circ}$ C, making it difficult for the batteries and electronics to maintain their performance. However, if the electronics are buried only a few feet in the snow, the temperature stays near -55°C year round. With careful insulation, the electronics can be kept warm enough to function. Since the noise from digital electronics can interfere with the antenna's sensitivity, the small preamplifier will be buried directly under the antenna, while the digital box will be buried up to 200 ft away. Therefore, the whole system consists of an antenna, preamplifier box, cable, and digital box which includes the batteries.

The noise of the system ideally should be below atmospheric noise so that all interesting signals would be captured. However, the atmospheric noise can be as low as 120 fT/ $\sqrt{\text{Hz}}$  at 80 Hz and 1.5 fT/ $\sqrt{\text{Hz}}$  at 1 kHz [6]. Therefore the noise floor of the system should be less than 1 fT/ $\sqrt{\text{Hz}}$  in order to detect all of the signals above the atmospheric noise floor.

These goals require a complete redesign of the analog, digital, and power supply of the system, as well as adding thermal insulation. This thesis describes the analog front end portion of the project, with emphasis on the preamplifier design.

In order to minimize the physical size and weight of the preamplifier, to meet the project goals described above, the preamplifier will be integrated onto a chip. The previous preamplifiers used in the old system used discrete parts, so this project is the first time the preamplifier is integrated onto a chip. Additionally, by reducing the numbers of parts and solder connections, the new preamplifier will be faster to build and will be more robust throughout the mechanical and temperature strain during shipping, deployment, and operation.

### **1.3** Previous Magnetic Sensors

There are a variety of magnetic sensors currently available for both research and commercial use. The sensors most relevant for this project are presented below. Typically these designs are not constrained by our strict power, sensitivity, and weight requirements, hence they are found to be unsuitable for this research project.

#### **1.3.1** Magnetic Sensors in Neural Research

Traditionally, the measurement of the magnetic fields created by nerve signals was performed using a toroid and a high impedance amplifier with feedback [11]. This system does get fairly good noise performance with a 100  $\Omega$  input impedance, however the noise figure increases dramatically at lower source resistances. An older neuron detector [19] uses CMOS probes and preamplifiers to detect neural signals between 100 Hz to 6 kHz with an amplitude up to 500  $\mu$ V. Since CMOS devices are very noisy below 1 MHz, a BiCMOS preamplifier with a 2.5 V supply for 1  $\mu$ V nerve signals has been developed [39]. Additionally this design uses a high input impedance circuit and expects a 1 k $\Omega$  input resistance. Decreasing the input impedance further with this approach would result in serious instability issues.

Another solution which also uses a toroid described elsewhere [54]. Here a high input impedance amplifier with feedback is used, achieving  $110 \text{ nA}/\sqrt{\text{Hz}}$  current noise at 1 kHz with a 1  $\Omega$  source impedance, which is much too large for this application. Additionally, no information was given on the power consumption, since it probably was not a design priority. Most current neural research with a noninvasive probe requires the use of a high input impedance system with a capacitive probe, for example [17] and [33]. Since the magnetic sensors have a low impedance, these neural sensors can not be used for this application.

#### 1.3.2 SQUIDs

SQUIDs (Superconducting Quantum Interference Devices) are used to measure small magnetic fields using a small loop antenna. These sensors are designed for low frequencies (<10 kHz) and can achieve very low noise, usually in the range of 1 fT–50 fT (sample systems include [9], [1], [58], and [7]). One particularly relevant application of a SQUID sensor is for mapping of underground features of the Earth [30], achieving a noise level down to 50 fT/sqrt(Hz), which is still above the 1 fT/ $\sqrt{\text{Hz}}$  needed for this research.

Since all of these devices require a very low operating temperature (0.3 K-77 K) to achieve the superconducting state, they require special cooling equipment and

liquid gas. A receiver system that is deployed in a remote location without access to external power can not accommodate the power consumption and weight to maintain the operating temperature, much less the supply of liquid gas. Additionally, this cooling equipment can cause noise problems in the range of 50–100 fT/ $\sqrt{\text{Hz}}$  [36].

### **1.3.3** Low Frequency Magnetometers

An early magnetometer is described in [23] where a ferrite coil is used to detect fields at 15 mT between 1.6 kHz and 50 MHz. In 1980, a system of three concentric loops was developed to achieve sensitivities down to  $-200 \text{ dB Gauss}/\sqrt{\text{Hz}}$  (1  $\mu\text{T}/\sqrt{\text{Hz}}$ ) at 100 Hz [27]. Another magnetometer was developed without a transformer for a high resistance (4.12 k $\Omega$ ) air coil, achieving 130 fT/ $\sqrt{\text{Hz}}$  sensitivity at 20 Hz [10]. A more recent design achieves 40 fT/sqrt(Hz) with a ferrite core coil, using feedback for impedance matching [36]. However, none of these systems are low power, and feedback systems are less robust with large temperature changes.

Another group has created a similar system for sensing magnetic fields with a transformer between the sensor and the amplifier [44]. However, they use a high input impedance amplifier with feedback. The result is a system that works between 600 Hz and 210 MHz.

None of these sensors achieve the required sensitivity, and most are not low power or integrated. The best frequency response and noise performance is achieved when the input impedance is low, as discussed in Section 2.2.2. However, most amplifiers designed for the applications discussed above use a high impedance op-amp with feedback. As the input impedance is lowered, the stability requirements make this topology choice difficult to implement. Instead, building a current amplifier directly allows for better stability and control for desired gain parameters, as well as reducing the power consumption, and is the preferred choice for this dissertation.

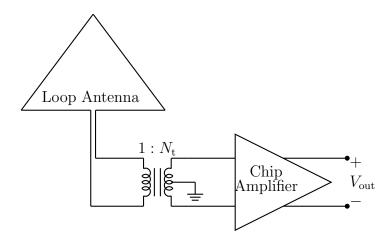

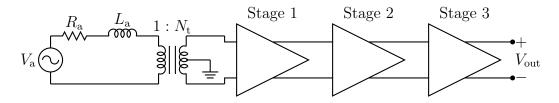

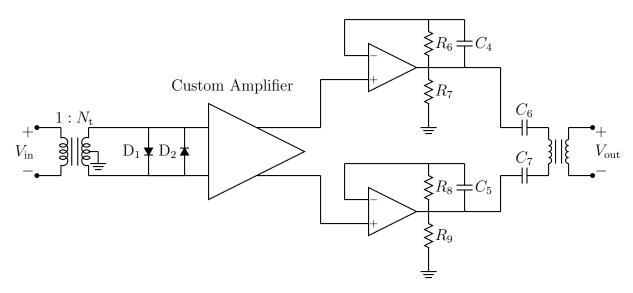

Figure 1.1: Front end of analog portion of receiver system including antenna, transformer, and amplifier. Full systems include two copies of the design with the antennas arranged orthogonally.

## 1.4 Analog Front End Overview

The analog front end of the receiver system includes the antenna, transformer, and amplifier, shown in Figure 1.1. Usually each system includes two channels that each have an antenna, transformer, and amplifier. The two antennas arranged orthogonally (often one is oriented in the north-south direction, and the other in the east-west). The data from the two channels can be used to determine the direction of arrival of the signals. For simplicity, only one channel is shown here. In ground-based magnetospheric research a large loop antenna is used to detect electromagnetic signals. A transformer steps up the signal voltage and DC isolates the antenna from the rest of the receiver. The antenna and transformer designs are discussed in Chapter 2.

The integration of the amplifier onto a chip significantly reduces the size and weight of the preamplifier, while reducing the soldering time for each board. However, a new amplifier design is required to meet the requirements in the new integrated environment. First, the receiver needs to have a flat frequency response over the bandwidth of the data, from 50 Hz to 30 kHz. If an amplifier with a low input impedance is used, the increase in induced voltage in the antenna with frequency is counteracted by the increase in inductive reactance of the antenna, making the current into the receiver flat with frequency. Although many of the other magnetic amplifier designs discussed above use a high impedance amplifier with a shunt resistor to lower the input impedance, the thermal noise of the shunt resistor degrades the noise performance significantly, making it impossible to meet the noise requirement with a 1  $\Omega$  input impedance. Instead, an amplifier that is designed to have a low input impedance, without any shunt resistor, is required to meet the receiver specifications.

#### **1.4.1** Amplifier Specifications

The specifications for the single chip amplifier are derived directly from the requirements of the project as a whole. The primary specification is the sensitivity because it determines whether scientifically interesting signals are detectable. With the 5 turn, 10 m base triangular antenna used for the receiver system, the 1 fT/ $\sqrt{\text{Hz}}$  magnetic field noise specification corresponds to a 7.8 pA/ $\sqrt{\text{Hz}}$  input current noise. A gain of at least 15 mV/nA is needed to ensure the signals are large enough to be digitized precisely. Since the batteries have to supply all the power for the system for a whole year, the power consumption of the parts is budgeted. Only 5 mW of power is available for the amplifier, which is a significant reduction from the 71 mW consumption in the preamplifier used in the old system. There are no commercially available integrated amplifiers that meet the power and sensitivity specifications, so a new custom amplifier is needed. Achieving these specifications for an integrated amplifier chip resulted in the contributions listed below.

### **1.5** Contributions

This work demonstrates the first integrated amplifier that meets the performance requirements for a VLF magnetic receiver. The amplifier achieves a 1.8 pA/ $\sqrt{\text{Hz}}$  current noise midband, and remains below the 7.8 pA/ $\sqrt{\text{Hz}}$  specification<sup>1</sup> between 234 Hz and 370 kHz. The gain also exceeds the specification between 90 Hz and 110 kHz, and reaches 35 mV/nA midband, while using less than 5 mW of power.

<sup>&</sup>lt;sup>1</sup>Corresponds to 1 fT/ $\sqrt{\text{Hz}}$  system sensitivity with a 5 turn, 10 m base triangular antenna.

Additionally, an optimization technique is developed to minimize the noise of the first stage, which can be used for any common base amplifier stage. The chip amplifier was field tested in Antarctica in a fully autonomous system and produced scientifically useful data for a year. A summary of the main contributions is listed below:

- Design of an integrated amplifier that meets the performance requirements for a VLF magnetic receiver.

- Development of noise optimization for bias current in a common-base topology.

- Implementation of the integrated amplified that achieves  $1.8 \text{ pA}/\sqrt{\text{Hz}}$  of current noise and 35 mV/nA of gain while using 4.8 mW of power.

## **1.6** Dissertation Organization

This dissertation presents the design and testing of the integrated amplifier as follows. Chapter 2 provides some necessary background on the antenna and transformer design, along with the basic relationships and noise characteristics of transistors. The design specifications and challenges is described in Chapter 3, and the design work to satisfy them is presented in Chapter 4. The noise optimization of the first stage is also included in the design chapter. Chapter 5 describes the testing methods and Chapter 6 presents the amplifier performance results. The integration of this amplifier into the rest of the magnetic sensor is discussed in Chapter 7, as well as the field test results. Finally, Chapter 8 provides the conclusions and suggestions for future work.

## Chapter 2

## Background

Before discussing the design of the amplifier and the rest of the analog portion of the system, the design of the antenna and transformer are presented. Their characteristics affect the noise performance of the entire system directly, so it is important to understand them well. A brief overview of the fundamental noise sources follows, and then finally the basic relationships of bipolar and MOSFET devices are reviewed.

## 2.1 Antenna Design

Magnetic field sensors are preferred at very low frequencies instead of electric field sensors mostly because they have superior noise response at the low end of the freqeuncy range. They are also less affected by nearby metallic structures and noise from snow, allowing for more accurate recording of the signal. Finally, magnetic field antennas do not require a ground plane, which simplifies their construction and calibration. The antenna and transformer designs were originally developed by Evans Paschal [35], and has been used in a large variety of low frequency magnetic receivers.

All magnetic antennas are constructed as a loop of wire, with either a high permeability (usually ferrite) core at the center, or nothing (air core). Antennas with a high permeability core are physically smaller, although not necessarily lighter, so they are often used where the space is the primary concern. However, their sensitivity can change with temperature, strong fields can cause a nonlinear response, and they are more difficult to calibrate [35]. Since the systems for this project are deployed in remote areas where the antenna size is not limited, large air core antennas are constructed and used on site.

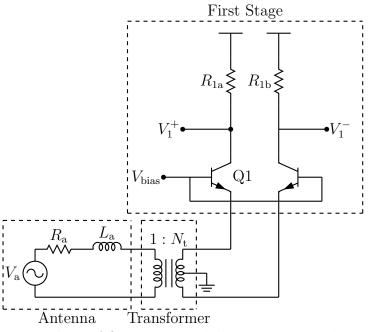

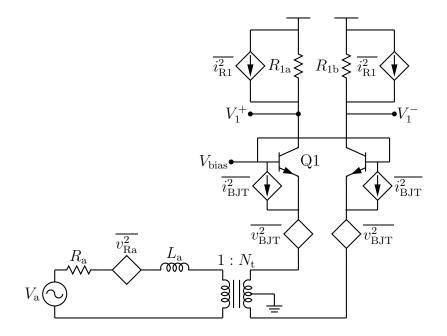

The model for the antenna is shown in Figure 2.1, along with the transformer and amplifier. The voltage source,  $V_{\rm a}$ , represents the induced voltage in the loop from the magnetic field. The inductor  $L_{\rm a}$  represents the coil inductance, and the resistor  $R_{\rm a}$  is the parasitic wire resistance.

Figure 2.1: System design of fully differential magnetic field receiver including antenna model, transformer model, and amplifier input impedance

### 2.1.1 Antenna Sensitivity

When designing an air loop antenna, there are three critical parameters: the area of the antenna  $A_a$ , the diameter of the wire d, and the number of turns  $N_a$ . These parameters determine the antenna wire resistance,  $R_a$ , and inductance,  $L_a$ , which in turn shape the system response and sensitivity. The winding capacitance and skin effect are negligible at frequencies below the megahertz range. It is therefore important to derive the relationship among the three parameters and the resulting sensitivity.

The loop shape is usually chosen based on its ease of construction and the desired area. A variety of common loop shapes are listed in Table 2.1. The constant  $c_1$  is related to the geometry of the antenna and allows for a general expression of the length of each turn that is valid for any shape:

Antenna Turn Length =

$$c_1 \sqrt{A_a}$$

(2.1)

| Shape of Loop            | $c_1$ | $c_2$ |

|--------------------------|-------|-------|

| circular                 | 3.545 | 0.815 |

| regular octagon          | 3.641 | 0.925 |

| regular hexagon          | 3.722 | 1.000 |

| square                   | 4.000 | 1.217 |

| equilateral triangle     | 4.559 | 1.561 |

| right isosceles triangle | 4.828 | 1.696 |

Table 2.1: Constants for various magnetic loop antenna shapes

Using this expression, the antenna resistance for any shape is

$$R_{\rm a} = \frac{4\rho N_{\rm a} c_1 \sqrt{A_{\rm a}}}{\pi d^2} \tag{2.2}$$

where  $\rho$  is the resistivity of the wire (for copper,  $\rho = 1.72 \times 10^{-8} \Omega m$ ) and d is the diameter of the wire. Adapting from [47, pp. 49-53], the inductance for any loop antenna is

$$L_{\rm a} = 2.00 \times 10^{-7} N_{\rm a}^2 c_1 \sqrt{A_{\rm a}} \left[ \ln \frac{c_1 \sqrt{A_{\rm a}}}{\sqrt{N_{\rm a}} d} - c_2 \right]$$

(2.3)

where  $c_2$  is also a geometry related constant, and can be found in Table 2.1 for a variety of loop shapes. The two variables  $R_a$  and  $L_a$  form the total impedance of the antenna  $(Z_a)$  that is the source impedance seen by the first stage of the receiver.

$$Z_{\rm a} = R_{\rm a} + j\omega L_{\rm a} \tag{2.4}$$

When an incident electromagnetic wave passes through the antenna, the voltage induced across its terminals is given by Faraday's Law:

$$V_{\rm a} = j2\pi f N_{\rm a} A_{\rm a} B \cos(\theta) \tag{2.5}$$

where  $V_{\rm a}$  is the voltage signal magnitude, f is the frequency, B is the magnetic flux density, and  $\theta$  is the angle of the magnetic field from the axis of the loop. If the axis of the loop is horizontal, the response pattern of the antenna is a dipole in azimuth.

For simplicity in the following design discussion, the field is assumed to be oriented normal to the antenna, and the term  $\cos(\theta)$  is omitted.

Since the size of a VLF receiving loop is very small compared to a wavelength ( $\lambda$ =1000 km at 300 Hz and 10 km at 30 kHz), the radiation resistance of the loop is negligible compared to the wire resistance  $R_a$ . Therefore, the minimum detectable signal is limited by the thermal noise of  $R_a$ . The sensitivity of the antenna,  $S_a$ , is defined as the field equivalent of the noise density; that is, the amplitude of an incident wave which would produce an output voltage equal to the thermal noise of  $R_a$  in a 1 Hz bandwidth. Using equation (2.5) the sensitivity (in units of T/Hz<sup>1/2</sup>) can be expressed as:

$$S_{\rm a} = \frac{\sqrt{4kTR_{\rm a}}}{2\pi f N_{\rm a} A_{\rm a}} \tag{2.6}$$

Note in equation 2.6 that the antenna sensitivity  $S_{\rm a}$  decreases with frequency (that is, the antenna becomes more sensitive). It is convenient to define a frequencyindependent quantity for comparing the performance of different antennas, thus the normalized sensitivity is defined as  $\hat{S}_{\rm a} = fS_{\rm a}$ . Using  $R_{\rm a}$  in equation (2.2), we find an expression for the normalized sensitivity that depends only on the physical parameters of the antenna:

$$\hat{S}_{a} = \frac{\sqrt{4kT\rho c_{1}}}{\pi^{3/2}d\sqrt{N_{a}}A_{a}^{3/4}}$$

(2.7)

This expression for sensitivity can be used to find the number of turns, antenna area, and wire diameter required for a target sensitivity at a specific frequency. The effect of the resulting antenna resistance and impedance on the rest of the system is discussed in later sections.

Further insight can be gained by expressing this sensitivity as a function of the mass of the antenna. The mass of the wire used in the antenna is found to be:

$$M = \frac{1}{4}\pi\delta c_1 d^2 \sqrt{N_{\rm a}} \tag{2.8}$$

where  $\delta$  is the density of the wire. Solving this for  $d\sqrt{N_{\rm a}}$  and substituting into (2.7)

produces normalized sensitivity:

$$\hat{S}_{a} = \frac{c_{1}\sqrt{4kT\rho\delta}}{2\pi\sqrt{MA_{a}}} \tag{2.9}$$

This interesting result shows that the only way to improve sensitivity with a given antenna material is to increase the total mass or area of the antenna. By expressing  $\sqrt{A_{\rm a}}$  in terms of the mass, the dependence of the sensitivity on the mass of the antenna is made clear:

$$\hat{S}_{a} = \frac{c_{1}^{2} d^{2} \delta \sqrt{4kT\rho\delta}}{8M^{\frac{3}{2}}}$$

(2.10)

This equation shows that the mass of the antenna is the fundamental tradeoff for the antenna sensitivity. Magnetic sensors are usually placed in remote areas to reduce interference from power lines (at 60 Hz and harmonics), so this tradeoff means that the sensitivity must be balanced against the practical weight limitations in shipping and construction of the antennas. The most severe limitations for these receivers are for units placed at the South Pole for research on electromagnetic waves in near-Earth space and the radiation belts. Since the Earth's magnetic field lines that pass through these regions in the upper atmosphere intercept the surface of the Earth near the polar regions, a ground-based receiver at the South Pole can detect the very low frequency signals of interest, while also taking advantage of the pristine low-noise environment due to the lack of other (man-made) noise sources.

### 2.2 Transformer

The transformer electrically isolates the antenna from the rest of the receiver and steps up the impedance by a factor of the turns ratio squared,  $N_t^2$ , to improve the impedance match to the preamplifier. Also, the low frequency cut-off of the transformer reduces the noise from the system at frequencies below those of interest. Figure 2.1 shows the circuit model for the transformer and the other equivalent noise sources from the amplifier.

### 2.2.1 Transformer Frequency Response

The combined transfer function of the antenna and transformer that relates the input voltage of the amplifier,  $V_{in}$ , to the induced voltage of the antenna,  $V_a$ , can be found with standard circuit analysis:

$$\frac{V_{\rm in}}{V_{\rm a}} = \frac{jwN_{\rm t}L_{\rm p}R_{\rm in}}{k_1k_2 + k_3} \tag{2.11}$$

where

$$\begin{aligned} k_1 &= [R_{\rm a} + R_{\rm p} + jw(L_{\rm a} + L_{\rm p})] \\ k_2 &= [(R_{\rm s} + jwL_2)(1 + jwC_{\rm s}R_{\rm in}) + R_{\rm in}] \\ k_3 &= jwL_{\rm p}N_{\rm t}^2(R_{\rm a} + R_{\rm p} + jwL_{\rm a})(1 + jwC_{\rm s}R_{\rm in}) \end{aligned}$$

Using equation 2.5 to relate the amplifier input voltage,  $V_{\rm a}$ , to the incident magnetic field, B, and simplifying, results in the approximate equation shown below.

$$V_{\rm in} \approx \frac{N_{\rm a} A_{\rm a} R_{\rm in} B}{N_{\rm t} (L_{\rm a} + pL_2/N_{\rm t}^2)} \left[\frac{f}{f - jf_{\rm t}}\right] \left[\frac{f}{f - jf_{\rm i}}\right] \left[\frac{-jf_{\rm c}}{f - jf_{\rm c}}\right]$$

(2.12)

where

$$f_{t} = \frac{(R_{a} + R_{p})||[(R_{s} + R_{in})p/N_{t}^{2}]}{2\pi(L_{a} + L_{p})}$$

$$f_{i} = \frac{R_{a} + R_{p} + (R_{s} + R_{in})p/N_{t}^{2}}{2\pi(L_{a} + pL_{2}/N_{t}^{2})}$$

$$f_{c} = \frac{1}{2\pi C_{s}R_{in}}$$

$$p = 1 + L_{a}/L_{p}$$

The various factors that have been isolated facilitate the understanding of how the transfer function is affected by both the design of the transformer and the input impedance of the amplifier. The factor p is the ratio of the total inductance on the primary side (including the antenna and  $L_p$ ) to the transformer primary inductance alone ( $L_p$ ). For an ideal transformer,  $L_p = \infty$ , and p=1. Below the frequency  $f_t$ , the shunting effect of  $L_p$  becomes important and the gain drops rapidly. The receiver is not useful in this region, making  $f_t$  the low frequency limit of the receiver response.

The input turnover frequency  $f_i$  is the frequency where the total resistance in the input circuit equals the inductive reactance. Note that  $f_i$  is much higher than  $f_t$  in a good design. Above  $f_i$  the impedance of the input circuit is dominated by the antenna inductive reactance  $2\pi f L_a$ . Even though the induced voltage across the antenna terminals (2.5) is proportional to frequency, the current in the input circuit above  $f_i$  is limited by the antenna reactance, which also increases with frequency, giving the output signal a flat overall frequency response. The wide bandwidth with a flat response simplifies the study of signals such as spherics and whistlers that span several decades of frequency.

At the frequency  $f_c$  the transformer secondary shunt capacitance  $C_s$  begins to short the input signal and the gain drops. The interval of flat frequency response is thus from  $f_i$  to  $f_c$ . Note that the transformer leakage inductance  $L_2$  does not significantly affect performance, because it appears in series with the much larger  $N_t L_a$ , as seen on the secondary side of the transformer.

### 2.2.2 Transformer Effects on System Noise

The main sources of noise in the system are the thermal noise of the antenna  $(\overline{v_{na}^2})$ , voltage noise of the amplifier  $(\overline{v_{n,amp}^2})$ , and the current noise of the amplifier  $(\overline{i_{n,amp}^2})$  (see Section 2.4.4 for amplifier noise model). The system sensitivity is directly affected by the transformer turns ratio and the ratio of current and voltage noise of the amplifier. For an ideal transformer:

$$S_{\rm sys} = \frac{\overline{v_{\rm na}^2 + \overline{v_{\rm n,amp}^2}/N_{\rm t}^2 + \overline{i_{\rm n,amp}^2}N_{\rm t}^2 Z_a^2}}{\omega N_{\rm a} A_{\rm a}}$$

(2.13)

Since the effect of the amplifier noise voltage is reduced by the transformer turns ratio while that of the noise current is increased, the choice of turns ratio has a direct effect on the sensitivity. Typically  $N_{\rm t}$  is chosen so that  $R_{\rm a}=R_{\rm in}/N_{\rm t}^2$ . In other words, the turns ratio is chosen to make the input impedance of the amplifier, as seen at the transformer primary, about the same as the antenna resistance in order to balance the low and high frequency noise concerns. With a common-base input stage, this turns ratio also means that  $\overline{v_{na}^2} \simeq \overline{v_{n,amp}^2}/N_t^2$ , thus making the low-frequency noise of the amplifier about the same as the thermal noise of the antenna. With this choice, the sensitivity improves with higher frequency for a decade or two above  $f_i$  until current noise  $\overline{i_{n,amp}^2}$  flowing through  $N_t^2 Z_a^2$  becomes important and the sensitivity levels off. Note that a common-base input stage of input resistance  $R_{in}$  gives much better noise performance than an actual resistor of size  $R_{in}$ , even if followed by a noiseless amplifier. The reason is that the current noise of the real resistor.

However, a real transformer adds some noise and changes the response. When the components  $L_{\rm p}$ ,  $R_{\rm p}$ ,  $L_2$ , and  $R_{\rm s}$  (as shown in Figure 2.1) are included, the total input referred voltage noise is:

$$\overline{v_{n,\text{tot}}^{2}} \approx \overline{v_{na}^{2}} + \overline{v_{n,p}^{2}} + \frac{\overline{v_{n,s}^{2}}}{N_{t}^{2}} p^{2} \left(1 + \frac{f_{\text{tn}}^{2}}{f^{2}}\right) + \frac{\overline{v_{n,amp}^{2}}}{N_{t}^{2}} \left[\left(p - \frac{f^{2}}{f_{\text{cn}}^{2}}\right)^{2} + p^{2} \frac{f_{\text{tn}}^{2}}{f^{2}}\right] + I_{n}^{2} N_{t}^{2} R_{a}^{2} \left(1 + \frac{(2\pi f L_{a})^{2}}{R_{a}^{2}}\right) \right]$$

(2.14)

where

$$f_{\rm tn} = \frac{R_{\rm a} + R_{\rm p}}{2\pi (L_{\rm a} + L_{\rm p})}$$

$$f_{\rm cn} = \frac{1}{2\pi \sqrt{C_{\rm s} N_{\rm t}^2 L_{\rm a}}}$$

To find the sensitivity, convert the input referred noise to the equivalent field using the antenna parameters:

$$S_{\rm sys} = \frac{\overline{v_{\rm n,tot}}}{\omega N_{\rm a} A_{\rm a}} \tag{2.15}$$

Comparing this result to the sensitivity of only the antenna in equation (2.6), the

sensitivity of the system is similar in form to that of the antenna by itself, with the antenna noise being replaced by the combined total noise of the antenna, transformer, and amplifier,  $\overline{v_{n,tot}}$ . At a given frequency, the receiver approaches ideal performance as the amplifier and transformer noise decreases toward the antenna thermal noise,  $\overline{v_{na}}$ .

The transformer has several important effects on the overall noise. The most important is the thermal noise from series resistances in the transformer,  $R_{\rm p}$  and  $R_{\rm s}$ , which add directly to the system noise. These resistances must be kept as small as possible to minimize the impact on the rest of the system. At low frequencies  $f^2/f_{\rm cn}^2 \to 0$  and the voltage noise is multiplied by the factor p. Therefore, for good low frequency noise performance, p must be kept small (i.e.  $L_{\rm p}$  made large). Also, at frequencies below  $f_{\rm tn}$ , the noise performance deteriorates rapidly, so  $f_{\rm tn}$  must be kept small. At high frequencies, more of the amplifier voltage noise appears across the transformer capacitance  $C_{\rm s}$  and increases the noise. So, for good high frequency noise performance,  $f_{\rm cn}$  should be kept large.

## 2.3 Antenna and Transformer Parameters

The previous Sections describe how the antenna and transformer both influence each other and the performance of the system, demonstrating that they must be designed conjointly as a unit, along with the amplifier input characteristics. The particular design used for this project is discussed below.

#### 2.3.1 Antenna Parameters

The antenna design must balance desired sensitivity with the practicality of construction. The resistance and inductance of the antenna from equations 2.2 and 2.3 affect the frequency response and sensitivity (2.12 and 2.15). A lower antenna resistance,  $R_{\rm a}$ , results in lower noise and better sensitivity (see equation 2.13), but requires wire with a larger diameter which becomes increasingly heavier. Additionally, increasing

| Base  | Wire           | $N_{\rm a}$ | $R_{\rm a}$ | $L_{\rm a}$ | $A_{\rm a}$ | $\hat{S}_{\mathbf{a}}$ |  |  |

|-------|----------------|-------------|-------------|-------------|-------------|------------------------|--|--|

| (m)   | AWG            |             | $(\Omega)$  | (mH)        | $(m^2)$     | $(V\sqrt{Hz}/m)$       |  |  |

|       | Square Antenna |             |             |             |             |                        |  |  |

| 0.160 | 20             | 47          | 1.002       | 0.998       | .02563      | $5.03 \times 10^{-3}$  |  |  |

| 0.567 | 18             | 21          | 1.006       | 0.994       | .3219       | $8.96 \times 10^{-4}$  |  |  |

| 1.70  | 16             | 11          | 0.987       | 1.013       | 2.892       | $1.89 	imes 10^{-4}$   |  |  |

| 4.90  | 14             | 6           | 0.972       | 1.029       | 24.05       | $4.13\times10^{-5}$    |  |  |

|       |                | Rig         | ght Isoso   | eles Tri    | angle       |                        |  |  |

| 2.60  | 16             | 12          | 0.994       | 1.005       | 1.695       | $2.97 \times 10^{-4}$  |  |  |

| 8.39  | 14             | 6           | 1.004       | 0.996       | 17.59       | $5.74 \times 10^{-5}$  |  |  |

| 10.0  | 14             | 5           | 0.999       | 0.975       | 25.00       | $4.84\times10^{-5}$    |  |  |

| 27.3  | 12             | 3           | 1.035       | 0.967       | 187.0       | $1.10 \times 10^{-5}$  |  |  |

| 60.7  | 10             | 2           | 0.959       | 1.043       | 920.9       | $3.22 \times 10^{-6}$  |  |  |

| 202   | 8              | 1           | 1.005       | 0.995       | 10164       | $5.97 \times 10^{-7}$  |  |  |

Table 2.2: Magnetic field antenna designs with 1  $\Omega$ -1 mH impedance. Two shapes are included, square and right isosceles triangle.

the number of turns (also increasing the weight), produces a larger antenna inductance,  $L_{\rm a}$ , thereby increasing the induced voltage for a given field (equation 2.5) and improves sensitivity (2.13). For this design, a 1  $\Omega$ -1 mH antenna impedance is chosen. This impedance balances the need for sensitivity, with the weight and construction time limitations during deployment.

Using equations 2.2, 2.3 and 2.6 a family of copper-wire loops of various sizes and sensitivities can be found, all with the same impedance. These antennas, listed in Table 2.2 for a 1  $\Omega$ -1 mH impedance, can be interchanged and used with the same receiver depending on the sensitivity required. Similar tables can be constructed for other impedance choices. The smaller antennas are more portable while the large antennas are more sensitive, so the antenna size used for a particular receiver is dependent upon needed sensitivity and available physical space. For example, a small antenna can be used with a receiver system to determine the best, low-noise site to construct a permanent, large antenna. However, not only are large antennas heavy and difficult to erect in remote areas, wind can also cause vibrations that can be mistaken for data variations. Large antennas should use a stiff frame to keep wind vibrations small. For large open triangular antennas supported by a central tower, the antenna wire should be kept slack so wind vibrations are below the frequencies of interest. For the measurements made in this dissertation, we used a five turn triangular antenna with a 10 m base which balanced the sensitivity and weight requirements, while the triangular shape simplified the construction.

### 2.3.2 Transformer Parameters

The primary focus for the transformer design is sensitivity. The turns ratio for the transformer,  $N_{\rm t}$ , is 16 and the primary inductance,  $L_{\rm p}$ , is 10 mH.<sup>1</sup> The high frequency response is dominated by the winding capacitance  $C_{\rm s}$ , which is 950 pF in this case. This capacitance is high because bifilar winding is used in both the transformer primary and secondary windings to assure balanced coupling. Using single-strand winding,  $C_{\rm s}$  can be much smaller.

The following parameters' values are calculated as described in equation 2.12.

$$p = 1.10$$

(2.16)

$f_{t} = 7.62 \text{ Hz}$

$f_{i} = 320 \text{ Hz}$

$f_{c} = 1.24 \text{ MHz}$

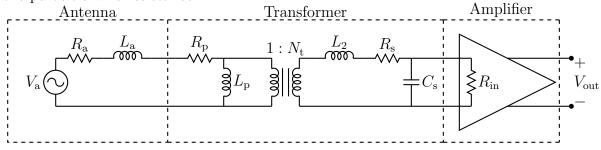

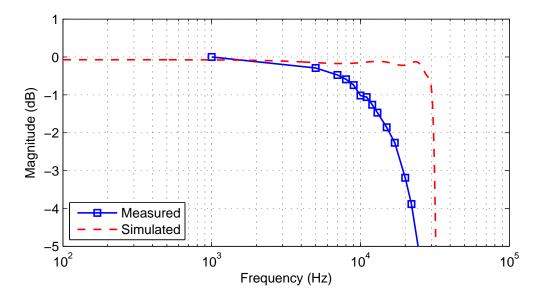

The voltage at the input of the amplifier terminals compared with the input magnetic field is depicted in Figure 2.2. The system frequency range is limited at the low end by  $f_{\rm t}$ , and at upper frequency by  $f_{\rm c}$ , resulting in an available bandwidth of 7.62 Hz – 1.24 MHz, well outside the required 50 Hz – 30 kHz bandwidth for the project. Also, for the noise performance of the transformer, the low frequency noise corner  $f_{\rm tn}$  is 14.5 Hz and the high frequency corner  $f_{\rm cn}$  is 10.2 kHz.

<sup>&</sup>lt;sup>1</sup>The transformers were designed and constructed by Dr. Evans Paschal.

Figure 2.2: Frequency response of antenna and transformer combined. The three frequencies that determine the bandwidth of the system,  $f_{\rm t}, f_{\rm i}$ , and  $f_{\rm c}$ , are depicted in red.

## 2.4 Noise Sources

Sensitivity is the most important specification for this amplifier, so the major noise sources that limit the sensitivity must be well understood. In this Section, we review the three main types of noise, all of which are present in the amplifier.

### 2.4.1 Thermal Noise

Thermal noise is generated by the random motion of electrons in any real resistor. The combined random motion of the electrons results in a noise current with the following noise power (from [29, p. 10]):

$$\overline{i_{\rm t}^2} = kT f \frac{1}{R} \Delta f \tag{2.17}$$

where k is Boltzmann's constant (1.38 x  $10^{-23}$  W-s/K), T is the temperature in Kelvin,  $\Delta f$  is the noise bandwidth, and R is the resistance. The noise power is constant for a pure resistor across the frequency spectrum (white noise). An equivalent voltage noise generated by the noise current is:

$$\overline{v_{\rm t}^2} = kT f R \Delta f \tag{2.18}$$

#### 2.4.2 Shot Noise

Shot noise is generated from the random arrival times of electrons when they cross an energy barrier, such as a p-n junction. It occurs in any device with a p-n junction such as diodes and all types of transistors. The noise power is also flat over frequency and is directly related to the DC current flowing through the junction ([29, p. 28]).

$$\overline{v_{\rm shot}^2} = 2qI_{\rm DC}\Delta f \tag{2.19}$$

where q is the charge of an electron (1.6 x  $10^{-19}$  coulomb).

#### 2.4.3 Flicker Noise

Flicker, or 1/f noise, inversely proportional to frequency, so it is referred to as "pink" noise. It is present in all transistors and some resistors when they have DC current flowing through them.

The origin of the noise has been under dispute. Some claim it is quantum in nature [14] and stems from the interaction of charge carriers with the photons they emit from lattice scattering. Although the 1/f noise relationship to the mobility can be explained this way, the most recent experimental evidence indicates that when the

lattice is damaged, the 1/f noise increases, while the mobility does not correspondingly change [16]. This evidence points to surface traps that capture charge carriers for a random amount of time and the bulk recombination of that charge [50] and [57]. The time constants of the release from the traps and the recombination generate the 1/f noise spectrum that increases with each lower decade of frequency [13] and [20].

The noise power is related both to the DC current density and characteristics of the fabrication of the device. The 1/f noise is in all forward biased p-n junctions, which in a BJT is the base-emitter junction. A common estimate of this noise is shown below [29, pp. 113-114]

$$\overline{i_{\rm f}^2} = \frac{K\Delta f}{f} \frac{I_{\rm B}}{A_{\rm j}} \tag{2.20}$$

where  $A_j$  is the area of the junction, f is the frequency, and the factor K is a constant empirically related to a particular fabrication process. The ratio of DC base current to the junction area implies the noise depends on the current density within the device. The current and physical size of the devices are the only means a designer has in reducing the 1/f noise of a device in a particular process, so it is important to choose a process with devices that have acceptable 1/f noise performance.

There is also 1/f noise in integrated resistors, and the noise power follows this relationship from [25, p. 254]:

$$\overline{i_{\rm f}^2} = \frac{KV^2 \Delta f}{f} \frac{R_{\Box}^2}{A} \tag{2.21}$$

where V is the DC voltage across the resistor DC and  $R_{\Box}$  is the sheet resistivity.

A common way to compare the flicker noise in a device is to measure the "noise corner" frequency. This frequency is the point when the flicker noise equals the other white noise of the device from thermal and shot noise sources. Above this point the thermal and/or shot noise dominates, while at frequencies below this point the flicker noise dominates. When designing circuits for low frequency applications, it is especially important to chose devices with a low flicker noise corner frequency, and if possible, the flicker noise corner should be below the frequencies of interest.

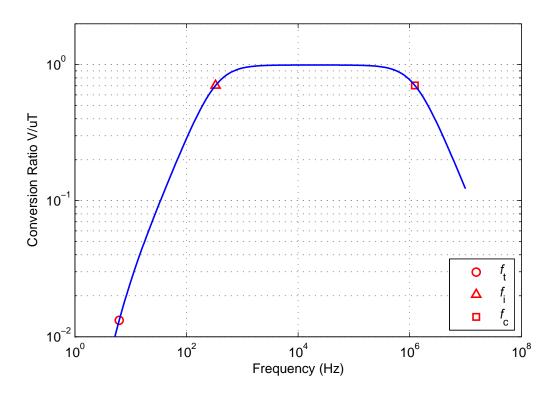

Figure 2.3: Noiseless amplifier with all noise combined into a voltage source,  $\overline{v_n^2}$ , and current source,  $\overline{i_n^2}$ .

### 2.4.4 Input Referred Noise of An Amplifier

In order to simplify noise calculations, all the noise of any amplifier can be modeled by two sources at the input of the amplifier, a voltage source,  $\overline{v_n^2}$ , and a parallel current source,  $\overline{i_n}$ , as shown in Figure 2.3 [29, p. 39]. The noise source  $\overline{v_s}$  is from the source resistance. The equivalent noise voltage is calculated by shorting the input so that the source resistance is zero, and calculating the total noise. If the input is left open so that the source resistance is infinite, the resulting noise is the current noise. Using this procedure, the noise in any circuit can be represented by only two sources, as shown in Figure 2.3.

To find the noise referred to the input signal, all the noise sources can be referred back as described in [8]:

$$(\text{Total Noise})^2 = (\text{source resistor noise})^2 + (\text{voltage noise})^2 + (\text{current noise} * \text{source resistor})^2$$

(2.22)

which in this case becomes:

$$\overline{v_{\text{tot}}^2} = \overline{v_{\text{s}}^2} + \overline{v_{\text{n}}^2} + \overline{i_{\text{n}}^2} R_{\text{s}}^2 + C \overline{v_{\text{n}} i_{\text{n}}} R_{\text{s}}$$

(2.23)

The correlation C between these two sources is negligible in most practical circuits [12, p. 768]. The result  $\overline{v_{\text{tot}}^2}$  represents the noise floor, which is the limit of the smallest signal that can be detected with that system.

### 2.4.5 Noise in Multiple Stages

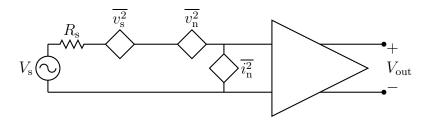

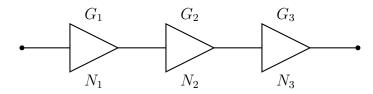

Figure 2.4: Amplifier with multiple stages, each with its own gain, G and noise power, N.

A multistage amplifier is shown in Figure 2.4. Each stage has a gain, G and contributes noise, N. The total output noise is easily calculated as

$$N_{\text{out}} = (N_1 G_2 + N_2)G_3 + N_3$$

=  $N_1 G_2 G_3 + N_2 G_3 + N_3$  (2.24)

Since the noise produced in the first stage is increased by the gains of all the subsequent stages, it is often the largest contributor to the total noise. Therefore, when designing a low noise circuit, minimizing the noise in the first stage is most important, while the noise in later stages can usually be neglected if the gains are large enough.

## 2.5 Transistor Models

The basic relationships of both bipolar and MOSFET transistors used in this work are reviewed below. These relationships provide the basis for the design calculations in Chapter 4. The noise properties of these devices are especially important in a low noise design, so the device noise models are also discussed.

### 2.5.1 Bipolar Transistor Characteristics

The collector current  $I_{\rm C}$  of a bipolar transistor is exponentially related to the baseemitter voltage  $V_{\rm BE}$ ,

$$I_{\rm C} = I_{\rm S} \exp\left(\frac{V_{\rm BE}}{V_{\rm T}}\right) \tag{2.25}$$

#### 2.5. TRANSISTOR MODELS

where  $V_{\rm T} = kT/q$ , k is Boltzmann's constant (1.38 x 10<sup>-23</sup> W-s/°K), T is the temperature in Kelvin, q is the charge of an electron (1.6 x 10<sup>-19</sup> coulomb), and  $I_{\rm S}$  is the saturation current. In all real BJT devices, the collector current also varies with the collector-emitter voltage  $V_{\rm CE}$ . This dependence is called the Early effect, and modifies the above idealized expression to the following:

$$I_{\rm C} = I_{\rm S} \left( 1 + \frac{V_{\rm CE}}{V_{\rm A}} \right) \exp\left(\frac{V_{\rm BE}}{V_{\rm T}}\right)$$

(2.26)

where  $V_{\rm A}$  is the early voltage, and  $V_{\rm CE}$  is the collector-emitter voltage.

The current gain of a bipolar device  $\beta$  is defined as the ratio of the collector and base currents:

$$I_{\rm C} = \beta I_{\rm B} \tag{2.27}$$

The base current,  $I_{\rm B}$ , determines the current gain and depends on the process and layout properties of the specific device. Since  $\beta$  is not a constant, it is important to find a region that is relatively constant in order to improve the amplifier linearity. There is always some small recombination of carriers in the base region which becomes significant when the collector current is also small. This increase in base current decreases  $\beta$ . At very high currents, the collector current is limited by high-level injection and the Kirk effect, and again reduces  $\beta$  [12, pp 24 – 26].

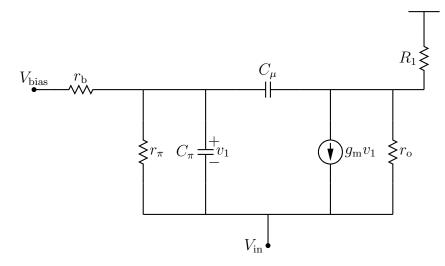

Figure 2.5: Small signal model of an NPN bipolar transistor.

A small signal model is used to clarify the gain relationships for the design process, and allows for noise and high frequency modelling. For small signals when the device is operating in the forward-active region, the transistor can be modeled as shown in Figure 2.5. The emitter current is modeled as a dependent source which is proportional to the base-emitter voltage and the transconductance,  $g_{\rm m}$ . The small signal transconductance depends only on the collector DC current:

$$g_{\rm m} = \frac{qI_{\rm C}}{kT} = \frac{I_{\rm C}}{V_{\rm T}} \tag{2.28}$$

The base-emitter resistance,  $r_{\rm pi}$  is:

$$r_{\pi} = \frac{\beta}{g_{\rm m}} = \frac{\beta kT}{qI_{\rm C}} \tag{2.29}$$

This model will be used to represent the bipolar transistors in the design discussion in chapter 4.

## 2.5.2 Bipolar Transistor Noise Model

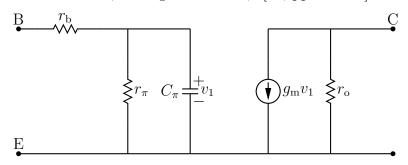

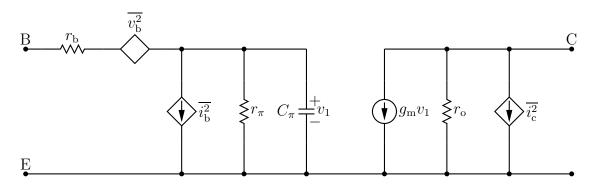

Figure 2.6: Noise model of an NPN bipolar transistor.

The small signal model discussed above can be expanded to include the noise sources. The noise model in Figure 2.6 shows the three largest noise sources,  $\overline{v_{\rm b}^2}$ ,  $\overline{i_{\rm b}^2}$ , and  $\overline{i_{\rm c}^2}$ . These noise sources are a large part of the total amplifier noise, and so are described in more detail below.

The base voltage noise  $\overline{v_{\rm b}^2}$  is from thermal noise in the base resistance,  $r_{\rm b}$ .

$$\overline{v_{\rm b}^2} = 4kTr_{\rm b}\Delta f \tag{2.30}$$

#### 2.5. TRANSISTOR MODELS

The base resistance is between the base contact and the active region between the emitter and collector, so it can be minimized with careful layout technique. The base current noise  $\overline{i_b^2}$  is a combination of shot and flicker noise.

$$\overline{i_{\rm b}^2} = 2qI_{\rm B}\Delta f + K\frac{I_{\rm B}}{fA_{\rm j}}\Delta f \qquad (2.31)$$

where  $A_j$  is the area of the base. The collector also has shot noise, resulting in the current noise  $\overline{i_c^2}$ .

$$\overline{i_{\rm c}^2} = 2qI_{\rm C}\Delta f \tag{2.32}$$

### 2.5.3 MOSFET Transistor Characteristics

MOSFET devices are used in the second and third stages, as well as the bias circuitry. In an ideal MOSFET device operating in saturation, the drain current is quadratically related to the gate source voltage.

$$I_{\rm D} = \frac{\mu C_{\rm ox} W}{2L} \left( V_{\rm GS} - V_{\rm th} \right)^2$$

(2.33)

However, because of channel length modulation, the drain current also depends on the drain-source voltage  $V_{\text{DS}}$ . To model this effect, the drain current equation is modified as follows:

$$I_{\rm D} = \frac{\mu C_{\rm ox} W}{2L} \left( V_{\rm GS} - V_{\rm th} \right)^2 \left( 1 + \lambda V_{\rm DS} \right)$$

(2.34)

where  $\lambda$  is the channel-length modulation coefficient and represents how much the channel varies compared to the fabricated length. The variation of the drain current (and therefore output impedance) of the transistor is a major source of nonlinearity when there is a large output voltage swing [38, pp. 25–27].

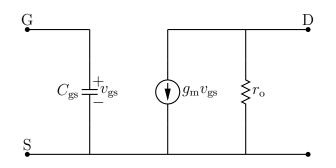

The small signal model is similar to the BJT and is shown in Figure 2.7. The transconductance is a measure of how the drain current changes with the gate-source voltage  $V_{\text{GS}}$ :

$$g_{\rm m} = \mu C_{\rm ox} \frac{W}{L} \left( V_{\rm GS} - V_{\rm th} \right) = \sqrt{2I_{\rm D}\mu C_{\rm ox} \frac{W}{L}}$$

(2.35)

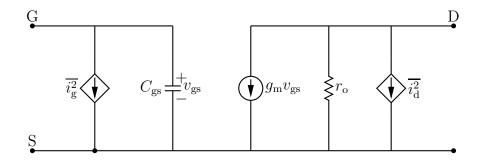

Figure 2.7: Small signal model of an NMOS transistor.

When channel length modulation is included, the transconductance becomes:

$$g_{\rm m} = \mu C_{\rm ox} \frac{W}{L} \left( V_{\rm GS} - V_{\rm th} \right) = \sqrt{2I_{\rm D}\mu C_{\rm ox} \frac{W}{L} \left( 1 + \lambda V_{\rm DS} \right)}$$

(2.36)

## 2.5.4 MOSFET Noise Model

Figure 2.8: Noise model of an NMOS transistor.

MOSFETs have two main noise sources shown in Figure 2.8,  $\overline{i_d^2}$  and  $\overline{i_g^2}$ . The drain current noise is a combination of thermal noise from the channel, and flicker noise.

$$\overline{i_{\rm d}^2} = 4kT\frac{2}{3}g_{\rm m}\Delta f + K\frac{I_{\rm D}}{fA_{\rm j}}\Delta f \qquad (2.37)$$

The drain current noise represents the majority of the noise in a MOSFET. However, there is some small leakage of current across the gate, creating a gate current,  $I_{\rm G}$ .

#### 2.5. TRANSISTOR MODELS

Since this gate current current is crossing an energy barrier, it has shot noise:

$$\overline{i_{\rm g}^2} = 2qI_{\rm G}\Delta f \tag{2.38}$$

At very high frequencies there is an additional component, which is generated by the thermal noise in the channel (and therefore correlated with the drain thermal noise). There are small changes in the local voltage produced as the charge carriers vibrate, which causes small capacitance changes, and results in an AC current through the gate. This current is in addition to the gate shot noise, and is frequency dependant [12, p. 759].

$$\overline{i_{\rm g,high\,frequency}^2} = 2qI_{\rm G}\Delta f + \frac{16}{15}kT\omega^2 C_{\rm gs}^2\Delta f \qquad (2.39)$$

# Chapter 3

# **Integrated Amplifier Challenges**

The performance of the amplifier chip is critical to the success of the project as a whole. This chapter discusses the requirements and challenges to achieve the needed performance. The amplifier requirements, which drive every part of the design work, are presented first. Because of the unique combination of requirements, there are several special challenges for this design which are discussed next. Finally, an overview of previous work demonstrates that only a new, custom amplifier chip is capable of meeting the specifications.

## 3.1 Design Requirements

The specifications for the amplifier are derived from the requirements of the project as a whole. In order to minimize the physical size, the amplifier is integrated onto a chip using National Semiconductor's 0.25  $\mu$ m BiCMOS process. This process has good low noise bipolar devices which are ideally suited for our application. As discussed in Section 2.2.1, the amplifier must have a low input impedance, because it improves the noise performance and keeps the receiver response flat in the chip bandwidth of 50 Hz–30 kHz. The amplifier's bandwidth easily extends beyond this specification on the high end, but 1/f noise presents the main challenge at the low frequencies.

The amplifier noise determines the sensitivity of the receiver, which determines the detectability of scientifically interesting signals. Therefore, the noise specification is the most important and must be met even at the cost of other performance metrics. Given the antenna and transformer design described in Section 2.3, the 1 fT/ $\sqrt{\text{Hz}}$  field noise specification for the project corresponds to a 7.8 pA/ $\sqrt{\text{Hz}}$  input current noise. A gain for the chip of at least 15 mV/nA is required to ensure the signals are large enough to be accurately digitized. The chip should be linear enough to produce spurious free signals at the output swing of 1 V. All of these specifications must be achieved with only 5 mW of power that is budgeted for the amplifier.

## **3.2** Amplifier Design Challenges

The unusual combination of specifications of low input impedance, low operating frequency, low noise, and low power creates several special challenges for this design. These challenges, described below, are the main reasons for the lack of any amplifiers that satisfy the requirements, as discussed in the next Section (3.3).

## 3.2.1 Bipolar Transistors Required

In order to realize the 1 fT/ $\sqrt{\text{Hz}}$  specification at low frequencies, low noise devices must be used in the first stage where the noise is most critical (see discussion 2.4.5). Although MOSFETs are the most common transistors used in integrated designs, their 1/f noise corners are in the megahertz range. The operating frequency range is for this amplifier is 4–5 orders of magnitude below the MOSFET's noise corner, resulting in 1/f noise that is prohibitively high.

The 1/f noise is large in MOSFETs because the gate field forces the channel current to flow very near the boundary to the oxide where the surface traps are, resulting in a very high rate of trapping. Alternatively, the current in bipolar transistors is more diffuse and flows in the bulk of the device away from the surface traps, resulting in much lower 1/f noise than MOSFETs. Also, bipolar devices have a larger number of carriers for the same current which also decreases the noise [49]. Because of the inherently much lower noise performance, bipolar transistors are ideally suited for this amplifier design. Because bipolar devices are less popular, it has been increasingly difficult to find a process for their fabrication. Fortunately, the recent interest in bipolar devices for their superior performance at high frequencies (research in the gigahertz range), has made processes with bipolar devices available, making the implementation of this amplifier in an integrated circuit possible for the first time.

## 3.2.2 No PNP Transistors Available

Although the process used for the amplifier implementation has good low noise NPN bipolar transistors, it does not support PNP transistors. This practical limitation is because most bipolar transistors are being used for high frequency applications, and then only for the input device of the first stage. By using PMOS devices as the load in the first stage, a fully complementary process is not needed. As discussed above, the very large 1/f noise of MOSFETs at VLF frequencies prevents their use in the first stage at all. With only NPN transistors and resistors, the available topologies are severely restricted for low noise amplifiers.

It has been suggested that a PMOS in a Darlington connection with an NPN BJT creates a pseudo PNP device (see [48]). The overall equation for this composite device is then:

$$I_D = -(\beta_F + 1)\frac{\mu_n C_{ox}}{2} \left(\frac{W}{L}\right) (V_{GS} - V_t)^2$$

(3.1)

from [12, p. 380]. However, this device suffers the same noise problems as using MOSFETs directly, so it can not be used in the signal path in the first stages.

#### 3.2.3 Stages Must be DC Connected

In most amplifiers stages are connected through an AC coupling capacitor, which allows the signal to pass, but keeps the stages DC isolated. Each stage has its own bias network which keeps it from being affected by slight changes in the DC level of the previous stage. However, to do so at low frequencies in an integrated design, the coupling capacitors would have to be many times larger than the whole chip in order for the impedance to be small enough to not affect the signal. Therefore, all the stages must be DC connected. In high gain amplifiers with DC coupling, even small changes in the DC level at the input can cause the whole amplifier to saturate, so the DC level of the signal path must be carefully controlled. Additionally, all the the biasing circuitry must be able to tolerate standard process and signal variations.

#### 3.2.4 Headroom

The supply voltage in modern processes has been dropping as MOSFETs shrink in size. The National Semiconductor process used for our design has a maximum supply voltage of 2.5 V. The base-emitter voltage,  $V_{\rm BE}$  must be around 0.7 V in order to be turned on (equivalently, MOSFETs need a similar gate-source voltage  $V_{\rm GS}$  of 0.8 V). In order for the relationships described in Section 2.5 to be valid (i.e. the devices in the proper operating region) their collector-emitter voltage  $V_{\rm CE}$  or drain-source voltage  $V_{\rm DS}$  must be over around 0.6 V. Consequently, only three transistors can be stacked vertically between ground and the power supply with all of them biased properly. The limited transistor stack eliminates many common amplifier topologies, such as emitter degeneration and cascoding. This topology restriction chiefly affects the DC control and linearity performance.

## 3.3 Previous Work

Because of the unique combination of requirements for this amplifier, each design from the relevant published work meets only a few of the specifications. Most standard amplifiers are fabricated in CMOS technology now (see overview of examples in [42]), even for low frequency applications such as gravity research [2], so most bipolar examples are from the 1980s.

Optical sensors that use photodiodes require a low impedance current amplifier for detection. One example that is implemented in a discrete design [55] achieves 15.3 pA $\sqrt{\text{Hz}}$  input referred noise, which is larger than the 7.8 pA/ $\sqrt{\text{Hz}}$ . A more recent example has a 7.4 pA/ $\sqrt{\text{Hz}}$  noise floor but uses 65 mW of power [34]. However, optical sensors are designed for the gigahertz frequency range, and the sensor designs are thus fundamentally different.

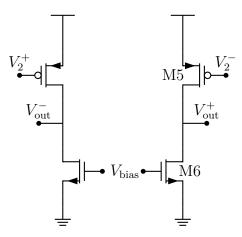

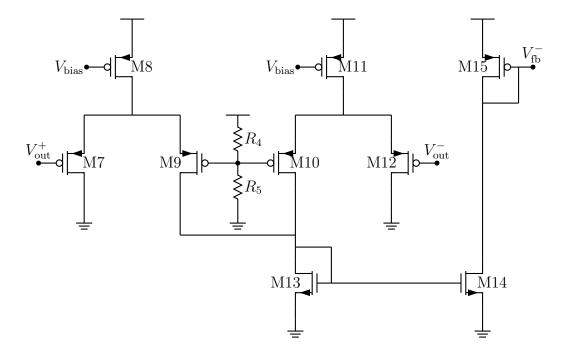

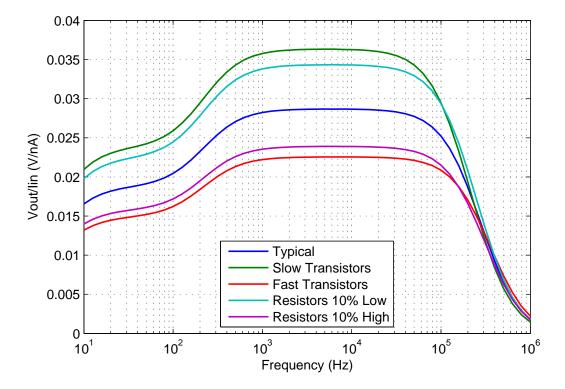

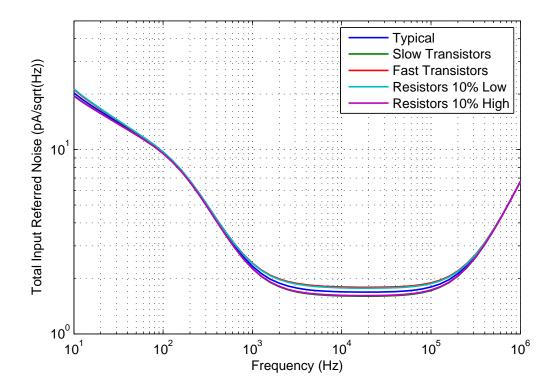

An audio range amplifier/instrumentation [8] uses complementary BJTs for good noise performance at low frequencies, however the common emitter topology for the input stage results in a high input impedance. The design achieves  $3.5 \text{ nV}/\sqrt{\text{Hz}}$ voltage noise and  $1.6 \text{ pA}/\sqrt{\text{Hz}}$  current noise at 10 Hz, but use 140 mW of power. Another BJT amplifier in the audio range achieves  $1 \text{ nV}/\sqrt{\text{Hz}}$  to  $3 \text{ nV}/\sqrt{\text{Hz}}$  at 10 kHz noise performance using a complementary BJT process [43]. But, with a high input impedance amplifier, and no power consumption listed, such a design would not work for our application.