# AUTONOMOUS ULTRA-LOW POWER ELF/VLF RECEIVER SYSTEMS

# A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Max Edward Klein November 2009

© Copyright by Max Edward Klein 2010 All Rights Reserved I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

(Umran Inan) Principal Adviser

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

(Ivan Linscott)

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

(Dwight Nishimura)

Approved for the University Committee on Graduate Studies.

This dissertation is dedicated to my parents Dana and John; to my sister, Meredith; and to my fiancé, Amanda.

# Abstract

ELF/VLF radio signals, from approximately 300Hz to 30KHz, are commonly used for submarine communications, ionospheric remote sensing, geophysical prospecting, and studies of the near-Earth space environment. Naturally occurring ELF/VLF emissions caused by nearly every lightning strike can be detected for thousands of miles and provide an abundance of wave-particle interaction possibilities in the radiation belts. Any applied studies of these events, however, require electromagnetic waves in the ELF/VLF band to be amplified, captured, analyzed, and stored. Specific studies often require the placement of receivers in extremely remote locations such as Antarctica or the middle of an ocean, and are almost always located far away from power sources to decrease noise. These scientific requirements drive the creation of new ELF/VLF receiver systems. Two new receiver systems were designed for use in terrestrial, typically Antarctic, locations. Both new systems utilize 10-100 times less power than the lowest-power comparable existing ELF/VLF receivers and were designed for remote unmanned operation in extreme environments without external power.

The so called Penguin system, comprised of a hybrid microcontroller and FPGA architecture, removes the overhead of a general purpose CPU to provide the most streamlined processing for data acquisition possible while still maintaining a relatively traditional sampling architecture. The drastically reduced architecture of the Penguin system, compared to traditional receiver systems, on average consumes less

power than a typical LED indicator lamp while capturing high fidelity ELF/VLF magnetic field snapshots every fifteen minutes. The low power and thermal requirements of the Penguin system enables low-cost remote studies of medium to large timescale phenomena such as Chorus and Auroral Hiss without the need for local power. The system has been deployed and operated at the United States Amundsen Scott South Pole Station in Antarctica.

A second ELF/VLF receiver architecture, the VLF Advanced Technology platform, or "VAT", removes the typical CPU from the sampling and recording loop further reducing power requirements and physical system size while gaining the ability to record continuously. This radically new architecture enables future scientific studies of the fine structure in time and frequency of long-term events, such as the onset mechanisms of natural Chorus emissions, due to the extremely low power requirements. The system architecture is also greatly applicable to any continuous time recording system, including but not limited to acoustic and electromagnetic arrays for subsurface imaging systems, ionospheric remote sensing, and optical sensors.

# Acknowledgements

The saying often goes something like "if you want to see the world, join the military." I guess whoever coined the phrase wasn't aware of the Stanford VLF group! Over the last five years I've been afforded the rare opportunity to visit and work in some of the most remote stretches of the planet, from Midway Atoll to midway down the South Pacific Ocean, culminating with the most extreme: the South Pole.

First and foremost, I would like to thank Prof. Umran Inan for bringing me into the VLF group. Even with a large group of students, he still made time to meet with everyone one-on-one every week. His tireless dedication to his students and VLF science is readily observable by all those around him and is truly appreciated. I would also like to thank Dr. Ivan Linscott for his advising, both technical and personal, throughout the Ph.D. program. Prof. Dwight Nishimura has my sincerest gratitude not only for being on my Ph.D. committee, but also for his mentoring of my teaching, especially with advice on dealing with tough classroom problems. The chair for my Defense, Prof. Per Enge, not only was kind enough to support my work and lead the discussion, but also taught one of the most interesting classes I took during my graduate education career. Behind the scenes, Dr. Maria Spasojevic and Dr. Dave Lauben provided invaluable insight and information on Antarctic ELF/VLF scientific studies, and general instrumentation and systems, respectively.

Over the years of outlandish ELF/VLF projects I have had the privilege to work with some of the finest engineers and students. At the forefront, Jeffrey Chang

provided consistent and excellent support, including system designs, schematics, board layouts, and debugging. Many of the projects would not have been possible without his dedication. I had the honor of learning an immense amount from Dr. Evans Paschal, our ultimate source for all things analog, and thank him for his extreme detail in explanations. Sarah Harriman, whose LNA is the front end of Penguin, provided significant help in moving Penguin from a bench-top recorder to a fully integrated receiver system. Charles Wang and Benjamin Mossawir were some of the best lab-mates one could ask for; I am grateful for their advice during the wee hours of the night. Bradford Bonney greatly aided in the construction of two buoys, along with Vikram Malhotra, Tim Su, Koji Gardiner, Daryl Ng, and Aaron Bronzan. Mark Gilbert, Yuhao Ding, and Wen Qi Chin provided excellent coding support during and after the 2007 REU program. Patrick Blaes did an amazing job for anyone, let alone an undergraduate, on Verilog coding of the modules used in the VAT CPLD, and continues to be an asset to our research group.

Last but certainly not least, I am eternally grateful to my family for their continued support throughout my academic career. For over 20 years my parents and sister have been there to push me forward, catch me when I fall, and support me in more ways than imaginable. My lovely fiancé Amanda has been amazing throughout the process, helping prod me to completion while continuously being so understanding of crazy schedules and esoteric terms. Thank you all.

Max E. Klein

Stanford, CA

September 2009

# Contents

| Abstract |      |        |                                         | $\mathbf{V}$ |  |

|----------|------|--------|-----------------------------------------|--------------|--|

| A        | ckno | wledge | ments                                   | ii           |  |

| 1        | Intr | oducti | on                                      | 1            |  |

|          | 1.1  | ELF/   | VLF Science                             | 1            |  |

|          | 1.2  | Sensin | g in Remote Locations                   | 2            |  |

|          | 1.3  | Uniqu  | e Receiver Requirements                 | 3            |  |

| 2        | VLI  | F Rece | iver Background                         | 6            |  |

|          | 2.1  | Termi  | nology                                  | 6            |  |

|          |      | 2.1.1  | ELF/VLF                                 | 6            |  |

|          |      | 2.1.2  | Broadband                               | 7            |  |

|          |      | 2.1.3  | Zero IF / Direct Conversion             | 7            |  |

|          |      | 2.1.4  | ENOB                                    | 8            |  |

|          |      | 2.1.5  | Firmware and Software                   | 8            |  |

|          | 2.2  | Receiv | rer Topology                            | 9            |  |

|          | 2.3  | Existi | ng VLF Receivers                        | 2            |  |

|          |      | 2.3.1  | AWESOME                                 | 2            |  |

|          |      | 2.3.2  | Automated Geophysical Observatory (AGO) | 4            |  |

|                                        |                         | 2.3.3                          | South Pacific Buoys              | 15 |

|----------------------------------------|-------------------------|--------------------------------|----------------------------------|----|

|                                        | 2.4                     | Existin                        | ng Receiver Limitations          | 18 |

|                                        | 2.5                     | Contri                         | ibutions of New Systems          | 20 |

| 3                                      | Pen                     | guin N                         | Micro-VLF Receiver               | 22 |

|                                        | 3.1                     | Backg                          | round $\ldots$                   | 22 |

|                                        | 3.2                     | 3.2 Derivation of Requirements |                                  |    |

|                                        | 3.3 System Architecture |                                |                                  | 27 |

|                                        |                         | 3.3.1                          | Background                       | 27 |

|                                        |                         | 3.3.2                          | Analog Front End                 | 28 |

|                                        |                         | 3.3.3                          | Sampling System                  | 30 |

|                                        |                         | 3.3.4                          | Time Keeping and Synchronization | 33 |

|                                        |                         | 3.3.5                          | Scheduler and Power Control      | 37 |

|                                        |                         | 3.3.6                          | Processing and Storage Systems   | 39 |

|                                        |                         | 3.3.7                          | Digital Hardware Architecture    | 44 |

|                                        | 3.4                     | Power                          | Budget                           | 45 |

|                                        |                         | 3.4.1                          | Battery Selection                | 48 |

| 3.5 Firmware and Software Architecture |                         | vare and Software Architecture | 51                               |    |

|                                        |                         | 3.5.1                          | System Firmware                  | 51 |

|                                        |                         | 3.5.2                          | System Software                  | 56 |

|                                        |                         | 3.5.3                          | Microcontroller Software         | 62 |

|                                        | 3.6                     | System                         | n Performance                    | 67 |

|                                        | 3.7                     | Deplo                          | yment Data                       | 71 |

|                                        | 3.8                     | Conclu                         | usion                            | 73 |

| 4                                      | VLI                     | F Adva                         | anced Technology Receiver        | 75 |

|                                        | 4.1                     | Backg                          | round                            | 75 |

|                                        | 12                      | Dorive                         | ation of Requirements            | 76 |

|                           | 4.3   | System Architecture                   |

|---------------------------|-------|---------------------------------------|

|                           |       | 4.3.1 Background                      |

|                           |       | 4.3.2 Sampling System                 |

|                           |       | 4.3.3 Processing and Storage Systems  |

|                           |       | 4.3.4 Digital Hardware Architecture   |

|                           | 4.4   | Power Budget                          |

|                           |       | 4.4.1 Battery Selection               |

|                           | 4.5   | Firmware and Software Architecture    |

|                           | 4.6   | System Performance                    |

|                           | 4.7   | Conclusion                            |

| 5                         | Fut   | ure Work 107                          |

|                           | 5.1   | Enhanced Flash Storage Media          |

|                           | 5.2   | VLF Interference Testing              |

|                           |       | 5.2.1 Voltage Regulators              |

|                           |       | 5.2.2 Flash Media Noise               |

|                           | 5.3   | Automatic Bias Voltage Adjustment     |

|                           | 5.4   | Integration of ASIC Signal Processors |

| $\mathbf{B}^{\mathbf{i}}$ | bliog | graphy 113                            |

# List of Tables

| 3.1 | Pin counts required for Penguin main system processor        | 43  |

|-----|--------------------------------------------------------------|-----|

| 3.2 | Power domains and estimated draw of Penguin peripherals      | 46  |

| 4.1 | Pin counts of VAT platform peripherals                       | 90  |

| 4.2 | Power domains and estimated draw of VAT platform peripherals | 94  |

| 4.3 | Measured VAT power domain 0 consumption                      | 104 |

# List of Figures

| 2.1 | Block diagram of a typical zero-IF VLF receiver    | 9  |

|-----|----------------------------------------------------|----|

| 2.2 | Block diagram of AWESOME receiver                  | 13 |

| 2.3 | Block diagram of a sample AGO receiver             | 16 |

| 2.4 | Block diagram of the South Pacific Buoy            | 17 |

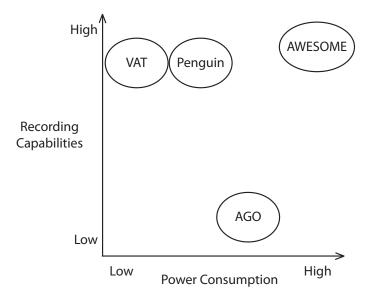

| 2.5 | Comparison of VLF Receiver Systems                 | 19 |

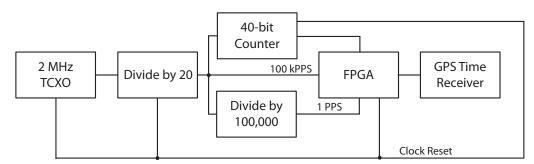

| 3.1 | Penguin Time Keeping System                        | 34 |

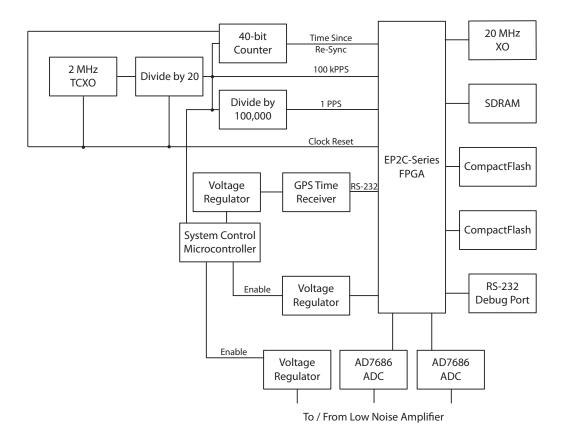

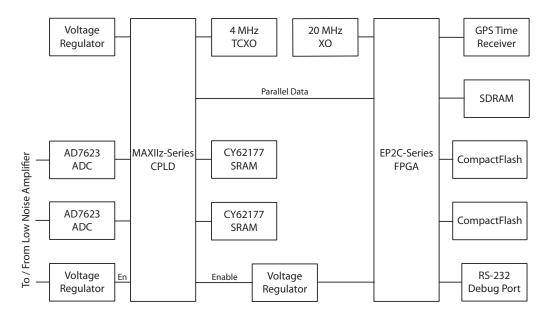

| 3.2 | Penguin Digital Architecture                       | 45 |

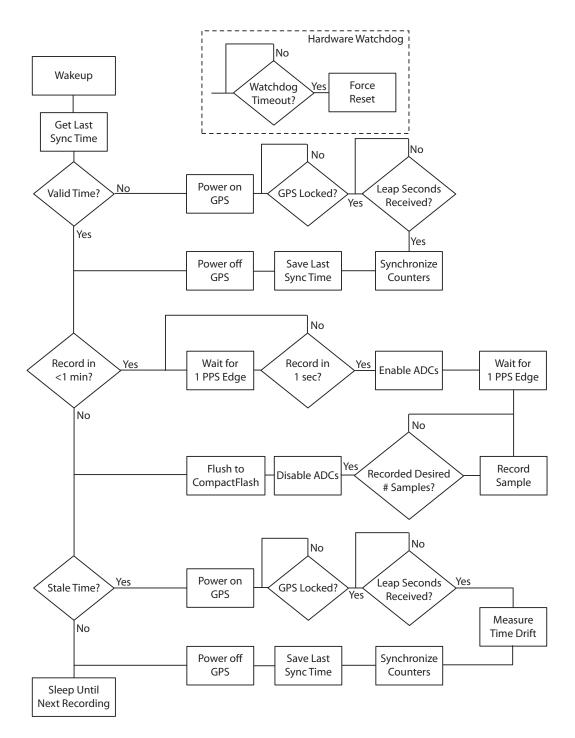

| 3.3 | Penguin Software Flowchart                         | 63 |

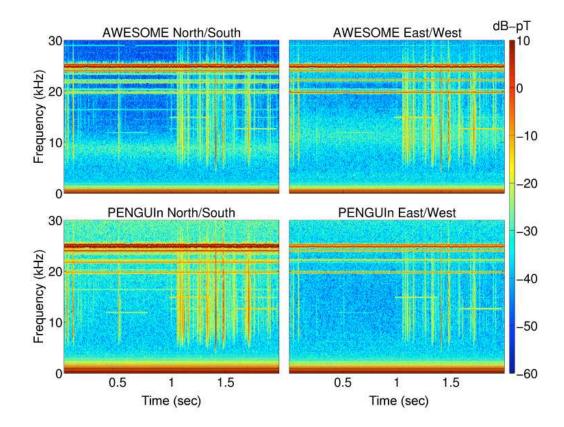

| 3.4 | Penguin and AWESOME Simultaneous Data              | 68 |

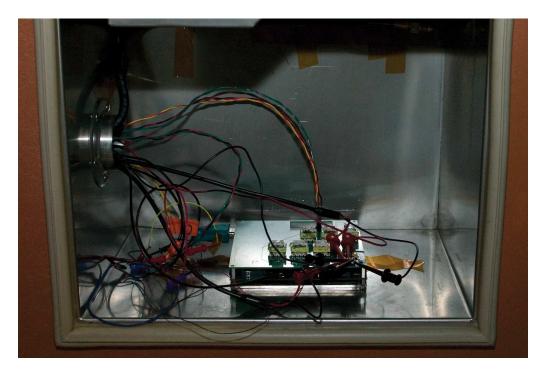

| 3.5 | Penguin System in Nitrogen-Flushed Thermal Chamber | 69 |

| 3.6 | Penguin Deployed at the South Pole                 | 72 |

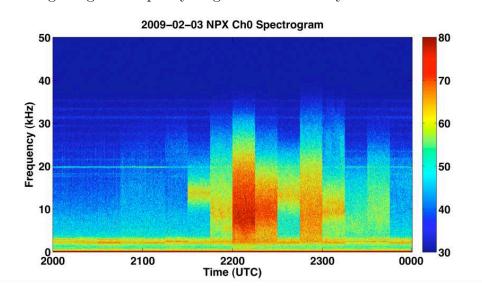

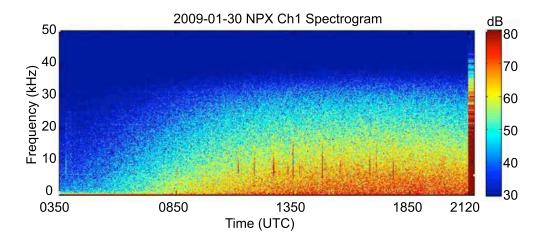

| 3.7 | Penguin Observation of Auroral Hiss                | 73 |

| 4.1 | VAT Digital Architecture                           | 93 |

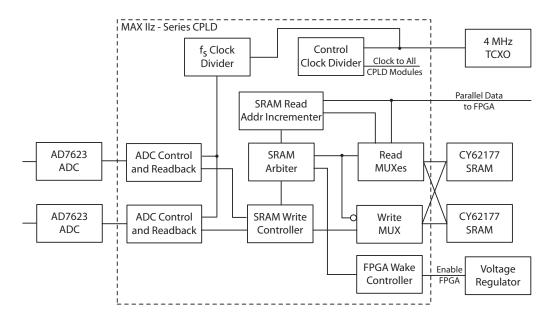

| 4.2 | VAT CPLD Architecture                              | 98 |

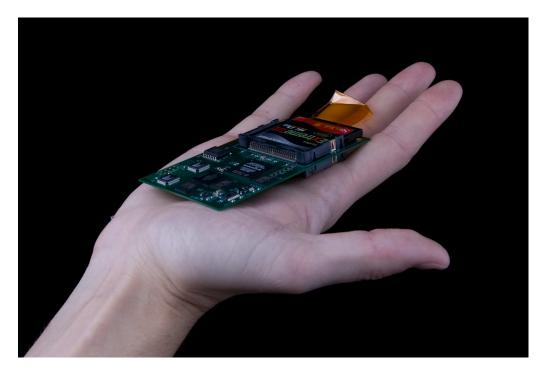

| 4.3 | VAT ELF/VLF Receiver                               | 06 |

| 5.1 | Penguin Data During Cool-down                      | 11 |

# Chapter 1

# Introduction

# 1.1 ELF/VLF Science

Extremely Low Frequency (ELF) and Very Low Frequency (VLF) radio emissions, both naturally occurring as well as man made, provide a rich phenomenological spectrum for investigative remote sensing of geophysical phenomena and the near-Earth space environment. These low-frequency signals, ranging from 300 Hz to 30 kHz, can be ducted along the Earth's magnetic field lines, causing ground-based transmission to travel through regions of the ionosphere, interact with particles in that area, and return as modified signals to the ground [13]. While staying on Earth, the ionosphere and Earth itself form a waveguide, allowing ELF/VLF transmissions to be ducted along the surface. While traveling through this Earth-ionosphere waveguide, pernerbations in the ionosphere or Earth's surface can result in changes in signal strength and phase, allowing sensing of lightning and other events over extremely long distances with a signal ELF/VLF receiver [62].

From the most polar locations on the planet, explorations of the far reaches of the Earth's ionosphere and magnetosphere are possible due to the shape of the Earth's magnetic field lines [49]. Studies are abundant in Antarctica, leading to a

better understanding of the Aurora, charged particle populations in the ionosphere, and the connectivity between the sun and Earth [26]. Experimental data is now available demonstrating how manmade transmissions can be used to intentionally alter the trapped particle population of the inner radiation belts [30]. All of these studies, however, rely on a common need for accurate, high-resolution ELF/VLF data to examine the natural and manmade environment, detect new events and phenomena, and provide ground-truth for theoretical models. The receiver systems capable of continuously receiving this data across the globe and recording them with high fidelity are the topic of this research.

## 1.2 Sensing in Remote Locations

ELF/VLF reception and recording location choices are driven by the scientific requirements of each individual study. As described above, these requirements often push the signal locations to high L-shells, or high geomagnetic latitude. Studies performed by Stanford University often take place in the far reaches of Alaska and across the Antarctic Plateau. Collecting data in these remote locations requires reliable systems that not only meet minimum signal sensitivity and signal integrity requirements, but are also capable of autonomous operation without human intervention or maintenance for extended periods of time.

A paradox exists in collecting ELF/VLF data. The instruments and receivers necessary all require power of some level to operate. However, the sites with the most pristine ELF/VLF environments are far away from power lines and generators, which can generate significant levels of ELF/VLF interference [43, 9]. The AWESOME receivers deployed in Alaska minimize this problem through both careful selection of the receiver sites as well as separation of the antennas and LNA from the remainder of the system, and local power source, by a significant standoff (Section 2.3.1). Some

of the most pristine, and scientifically interesting, ELF/VLF receiver sites occur in Antarctica [22]. In these ultra-remote locations, neither power lines nor generators are present, requiring any instrumentation to contain its own power source. While solar may produce significant amounts of power during the summer months, the nearly 6 months of total darkness do not make this a viable option for continuous power. Minimizing the required system power is paramount for the success of such installations.

Many sites, such as those in Alaska, may be close to human populations who can occasionally swap and mail hard drives or other storage media for mass data transfer back to the science community. Other locations, especially polar sites, are without significant local bandwidth, internet or otherwise, and may not even have a human population present for the majority of the year. AGO field sites, described in Section 2.3.2, are totally unattended except for occasional visits dedicated to system maintenance, occurring once every few years. Clearly, these locations represent some of the most challenging environments to collect scientific data, and are largely unexplored due the the current unavailability of low cost, low mass, low power reception systems. New instruments are essential for massive data gathering operations in these regions.

# 1.3 Unique Receiver Requirements

Reception and storage of ELF/VLF signals fall into a unique regime in terms of signal bandwidth and required fidelity. A broadband ELF/VLF receiver is required to sample at 100 kHz with 16-bit resolution, as discussed in detail in Chapter 2. This sampling requirement fits uncomfortably between existing Supervisory Control And Data Acquisition, or SCADA, networks and traditional radio receivers. SCADA networks, typically used for industrial monitoring and control applications, have

significantly slower data rates, typically around several kilobits per second [38, 8]. Due to this significantly slower data rate, simple power saving measures, such as turning on and off the sensor and/or processor between samples, is more practical than with ELF/VLF reception. Conversely, modern software defined radios typically have a much higher bandwidth, and thus demand extremely fast analog to digital converters and high powered commodity processors [10].

The unique bandwidth of ELF/VLF reception systems leaves a gap in traditional power optimization mechanisms and architectures, especially when coupled with the need for low electromagnetic emissions within the 300 Hz to 30 kHz band. Baseline receiver systems, detailed in the next chapter, are able to provide good quality data, but are impractical for widespread deployment in extreme and remote environments due to power limitations.

Two new receiver systems, including a revolutionary new sampling architecture, are presented in the following chapters. These two systems each reduce the power requirements of existing ELF/VLF receiver systems by over one order of magnitude, while maintaing or exceeding parity in data quality. The first system, Penguin, utilizes a traditional receiver and sampling architecture with a highly customized processor, optimized for ELF/VLF sampling and recording tasks. Penguin is operational on the Antarctic Plateau near the South Pole as a totally self-contained unit weighing less than 50 pounds total, with a majority of the weight due to mechanical structures; the batteries themselves weigh under 20 pounds.

The second receiver system, the VLF Advanced Technology receiver, or VAT, removes the traditional general purpose CPU from the sampling loop, dramatically reducing power consumption while still enabling continuous, real-time sampling of multiple ELF/VLF broadband channels. VAT reduces the continuous average power consumption by fivefold from the Penguin system, creating the smallest and most power efficient ELF/VLF receiver system known at this time. This revolutionary

sampling system architecture provides better than order of magnitude power improvement, and is generally applicable to many mixed-signal sampling systems of similar bandwidth.

Both Penguin and VAT enable new scientific studies that were not previously possible with existing instrumentation. The dramatic reduction in power consumption and physical footprint allow these systems to be deployed in some of the most remote locations on the planet. Extensive lab testing and field demonstrations indicate that the systems as designed are capable of operating unattended in the coldest naturally occurring climates on Earth while maintaing proper operation. With these new capabilities, large distributed interferometric arrays are now possible on the Antarctic Plateau or anywhere else on Earth with low cost hardware and greatly reduced deployment complexity and expense.

# Chapter 2

# VLF Receiver Background

In order to have an in-depth discussion of VLF receivers at the system level, it is critical that a common vocabulary be established. The required background includes generic radio and electronic terms as well as a primer on traditional direct conversion VLF receiver topology. Once the terminology is established, a review and discussion of existing systems will provide the requisite background to identify prior shortcomings and underscore the contributions of the system described in this work.

## 2.1 Terminology

## 2.1.1 ELF/VLF

ELF/VLF literally stands for Extremely Low Frequency / Very Low Frequency, and refers to two specific bands in the RF spectrum. In the telecommunications community, ELF is defined as frequencies between 3 Hz and 30 Hz, while VLF is defined as 3 - 30 kHz, however in the scientific community ELF is the region between 300 Hz and 3 kHz, while VLF is 3 kHz to 30 kHz [60]. Since this paper is

directed at the scientific and academic community, it will use the later convention, and may also refer to an ELF/VLF receiver as simply a "VLF" receiver for brevity. In ITU / telecommunication terms, the discussed receivers are technically ULF/VLF receivers. All systems discussed in this paper thus cover the 300 Hz to 30 kHz band unless explicitly stated otherwise.

#### 2.1.2 Broadband

A VLF receiver is said to be "broadband" if it records the entire ELF/VLF band, nominally 300Hz to 30KHz as defined by the scientific community. This contrasts to a narrowband receiver, such as components of the AGO system described in Section 2.3.2, which sample only a small frequency range which is totally contained within this band. As a practical matter, the broadband ELF/VLF receivers discussed in this paper sample at 100 ksps unless otherwise noted. This oversampling, in relation to the Nyquist rate, allows for finite filter roll-off and provides greater alias rejection [35]. Note that while the temporal, and thus frequency, resolution is specified by the "broadband" qualifier, the amplitude resolution and bandwidth are not. All systems discussed contain a 16-bit digitizer, unless otherwise stated. This does not, however, imply that collected data necessarily has 16 ENOB (see Section 2.1.4).

## 2.1.3 Zero IF / Direct Conversion

All discussed broadband ELF/VLF receiver systems are direct conversion, meaning that the raw RF signal is amplified, filtered, and then directly digitized and/or recorded [1]. In contrast to a heterodyne system, where the RF signal is mixed with a local oscillator to an Intermediate Frequency (IF), a direct conversion receiver does not require any RF oscillators to operate, resulting in significant power and cost savings [48]. "Zero IF" is generally synonymous with direct conversion, as it

alludes to an intermediate frequency of zero, or no frequency shifting of the original signal. Due to the relatively low carrier frequencies of VLF, modern analog-to-digital converters are more than capable of sampling sufficiently fast to capture the entire ELF/VLF band without downconversion.

#### 2.1.4 ENOB

The Effective Number of Bits, or ENOB, is a measure of the effective resolution of an ADC, and is tested by injecting a single sine wave and examining the output. The ENOB is directly related to the decibel SINAD, or Signal to Noise And Distortion, of a sinusoidal test signal and is expressed in units of bits. Note that the system-wide ENOB is dependent upon the amplitude of the stimulus signal. Thus, a poor RF front-end connected to an extremely high performing ADC may result in a system-wide ENOB lower than that of a poorer performing ADC but with a better front-end. From the equation, it is clear that anything harming the SNDR or SINAD of the system will also adversely impact the ENOB as revealed in Equation 2.1.

$$ENOB = \frac{SINAD_{dB} - 1.76}{6.02} \tag{2.1}$$

#### 2.1.5 Firmware and Software

In the discussions of digital system architectures, both firmware and software will be covered. To avoid confusion, these two terms must be explicitly defined for our local context. Firmware signifies the arrangement or interconnection of electrical logic. Both Field Programable Gate Arrays and Complex Programable Logic Devices contain firmware, which describes how their respective logic fabrics are configured. Software is defined to be codes running on a given hardware processing unit. Software encompasses the programming that is executed inside of a microcontroller,

on a personal computer, as well as that executed within a CPU that is defined in an FPGA. The implementation of the CPU itself on an FPGA, however, is considered to be firmware.

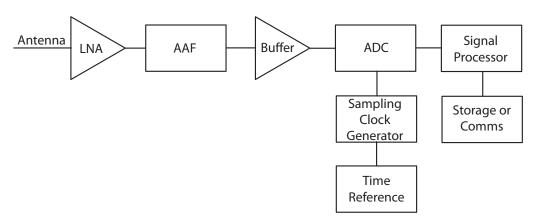

## 2.2 Receiver Topology

A typical broadband VLF receiver, shown below in Figure 2.1, consists of an antenna, Low Noise Amplifier (LNA), Anti-Aliasing Filter (AAF), a time reference, and a recording or communications device. In a digital VLF receiver, which will exclusively be discussed in this paper, the recording or communications devices consists of an analog-to-digital converter (ADC) plus a processing device and storage or communications channel. Historically, the LNA is placed as electrically close as possible to the antenna to reduce the amount of cable losses before the received signal is amplified. The remainder of the system, from the AAF through the storage or communication system, is placed further away, greatly reducing the received system noise from these components through the antenna.

Figure 2.1: Block diagram of a typical zero-IF VLF receiver

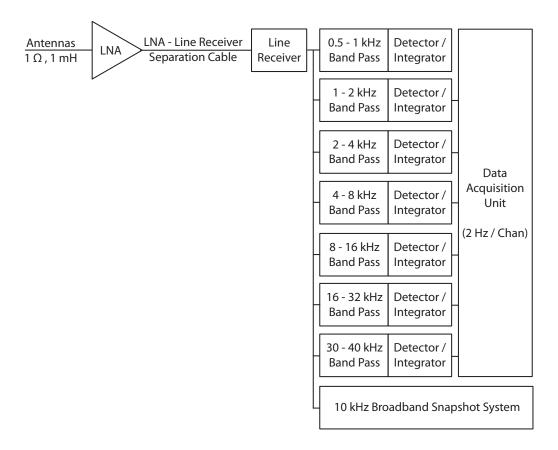

Narrowband VLF receivers have several different architectures depending on the

desired frequency resolution and power constraints. One type of receiver, often referred to as "channelized," has a bank of bandpass filters just after the buffer and before the ADC. Each bandpass filter only passes the frequency range desired for a particular channel, with both the center frequency and bandwidth set by scientific requirements. The output of each bandpass filter can then be fed to an integrator to allow for extremely slow sampling, often with a sampling rate of around 1 Hz. This low sampling rate allows for ultra-low power computational systems and minimal storage requirements. The analog bandpass filters also can consume significant amounts of power due to the amplification required to maintain the desired signal strength through an array of many parallel bandpass filters. One example of such a system is the Automated Geophysical Observatory, explored in more detail in Section 2.3.2. Unfortunately the data collected from this type of narrowband architecture typically has a frequency resolution of several kHz and temporal resolution of around 1 second. While adequate for many scientific studies of natural phenomena, this low resolution data is unable to capture fine structure in time or frequency, and thus is unable to record or reproduce the full detail of the received events.

Another narrowband architecture with significantly greater resolution is targeted at receiving manmade ELF/VLF transmissions. This type of narrowband receiver locks onto a manmade transmitter, demodulates and removes the data from the carrier wave, and then exclusively examines the carrier itself. Currently, the demodulation of the signal can be performed readily by commodity PC hardware, as is the case with the AWESOME receiver discussed in Section 2.3.1 (note, however, that this receiver is also capable of full broadband ELF/VLF reception as well). This receiver class is useful for scientific studies where the behavior of natural phenomena is observed through amplitude and phase changes of VLF transmission paths across the world [41]. For these studies to be accurate, especially if multiple

sites are used for interferometry such as with the Holographic Array for Ionospheric Lightning Research, the transmission sources must have a highly accurate and stable carrier wave, as is true with many naval transmitters, and the receivers must have a similarly accurate and stable time and frequency base, as is the case with GPS-synchronized receivers [32]. With these conditions met, the low data rate narrowband data can be integrated over minutes or hours to detect extremely small changes in the wave propagation path.

With any of the receiver topologies discussed so far, there is still a choice as to when a system should record and for how long. A continuously sampling full broadband system with all three possible magnetic axes being received would consume a considerable amount of power and recording space. For example, assuming 16-bits per channel per sample with a 100 kHz sampling rate, nearly 52 gigabytes of data would be collected each day from each receiver. With modern storage technologies, this vast quantity of data can be stored provided the storage medium is able to be exchanged every few weeks. For remote sites, like those in Antarctica, the extreme reaches of Alaska, or autonomous platforms in the ocean, this is not practical, and mechanisms of data reduction are required.

The easiest method to both reduce the quantity of data collected as well as possibly the energy consumed by the receiver is to simply cycle the recording on and off. Such a synoptic recording schedule is used in the AGO system for its broadband snapshots while the lower data rate narrowband data is continuously recorded. Another method is to only have the receivers operating when the researchers are expecting events to occur. Scheduling of the recording periods is done both with the South Pacific Buoys (Section 2.3.3) as well as the AWESOME systems. Lastly, the huge amount of broadband data can be compressed for instance by either decimating it to remove higher-frequency components that are not of interest during a particular experiment, or to save a processed snapshot of the data for evaluation.

The buoys both decimate the data to an effective sample rate of 10 kHz, due to the low-frequency nature of the experiments, and are able to store both raw data as well as a JPEG image of a spectrogram of any given section of the data, greatly reducing the data transfer required to analyze signals from the extremely remote platform.

These and other data reduction techniques are particularly prevalent on remote, power-constrained, autonomous ELF/VLF receiver platforms. As discussed throughout this paper, while storage capacity has been increasing at great speeds, maintaining the lowest power possible while operating in some of the harshest climates on Earth is still a significant challenge. We will briefly look at the current "gold standard" of VLF data quality, the AWESOME receiver, as well as two previously deployed autonomous receiver systems. With the benefits and limitations of these systems understood, we then proceed to describing two different receiver platforms, the subject of this dissertation, that greatly increase data collection capabilities in extreme environments.

## 2.3 Existing VLF Receivers

#### 2.3.1 **AWESOME**

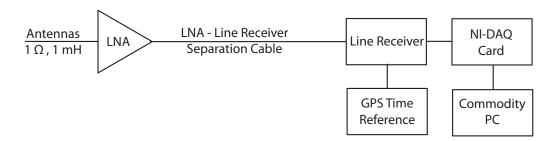

The AWESOME receiver, or the "Atmospheric Weather Educational System for Observation and Modeling of Electromagnetics," is a ground-based ELF/VLF receiver system. The AWESOME system is extremely sensitive, capable of receiving signals as low as several tens of femtoTesla per root Hertz, with true broadband coverage of 300 Hz to nearly 50 kHz [29]. The receiver typically consists of two large crossed loop magnetic field antennas with a co-located preamplifier or LNA. The antennas and LNA are impedance matched and sized to obtain the maximum sensitivity, limited primarily by atmospheric or local noise. The antennas and LNA are connected

by a significant length of Belden shielded multi-conductor cable to an indoor line receiver supporting data acquisition. This cable allows the antenna to be located a significant distance away from the rest of the system, and preferably away from power lines, generators, and any other sources of ELF/VLF interference. The line receiver filters the signals, digitizes them with a COTS sampling system into a PC, and runs custom software to control the sampling intervals, perform any processing such as narrowband extraction, and record the data to disk or to a remote site. A block diagram of the AWESOME receiver system is shown in Figure 2.2.

Figure 2.2: Block diagram of AWESOME receiver

The system is relatively inexpensive to produce, and benefits from a GPS-synchronized sampling clock, allowing for widespread interferometric use [52]. While the system produces superb data quality and is the baseline of quality for many new systems, it is limited in deployment locations. The system requires nominally 30 Watts not including the PC, or conservatively estimated at 60 Watts total when combined with a current laptop. Most deployments, however, use a regular desktop PC plus external hard drives for data transfer, equating to over 200 Watts of power. This high power requirement limits AWESOME receivers to locations with generator or

AC line power. Unfortunately, these locations also will typically have a higher background ELF/VLF noise level than those without local power. Extremely remote locations, including some islands and most of the Antarctic Plateau, are unsuitable for AWESOME deployments.

The AWESOME system contains a traditional direct-conversion broadband receiver topology as detailed in Section 2.2. For its particular implementation, the ADC is a National Instruments Data Acquisition, or NI-DAQ, Card contained in a PC, sampling at 100 kHz with 16-bit resolution, timed off of a GPS synchronized clocking circuit. Likewise, all signal processing and recording takes place in the same COTS computer. The AAF is an active circuit, allowing for extremely sharp filter roll-off and minimal signal loss, but at an obvious cost in required power. The LNA and antennas are matched to a nominal 1 ohm, 1 milliHenry impedance, which is a standard used in all other system discussed in this document.

### 2.3.2 Automated Geophysical Observatory (AGO)

The Automated Geophysical Observatory is a decades-long experiment to study phenomena at high geomagnetic latitude. Of particular interest is the current AGO VLF receiver system, deployed as a subsystem of the AGO electronics in the mid 1990s [54]. This VLF receiver provides synoptic "broadband" data with initially 2.5 kHz bandwidth, and more recently 10 kHz bandwidth, as well as several configurable channelized feeds. Both the broadband and narrowband data are filtered in analog, allowing for minimal computational requirements. The narrowband channels are of varying bandwidths between 500 Hz and 16 kHz, which are integrated and sampled at up to 2 Hz. A representative AGO system block diagram is shown in Figure 2.3. The extremely low sampling rate reduces the storage requirements of the system, which often must operate for a year or more unattended, and only have low data rate Iridium connections for communications. Aliasing on these channels does not

occur since the 500 - 16,000 Hz bandwidth is integrated prior to sampling, however the temporal resolution of events is limited to 0.5 seconds and the frequency resolution is equivalent to a particular channel bandwidth. High temporal and frequency resolution data are available from the AGO system during the synoptic recording periods, but are limited to a maximum frequency of 10 kHz and only currently record for one minute out of every fifteen minutes.

The VLF portions of the AGO system consumes approximately 30 Watts, allowing for the system to operate on the Antarctic Plateau with onboard power, but requiring extremely costly maintenance trips each year to provide more fuel for the power system. The system is also housed in a temperature-controlled hut, and is not currently rated for outdoor use without additional protection. The AGO system has provided a plethora of scientifically-useful data from Antarctica for a number of years. The great expense of installing and maintaining each AGO site, coupled with the lack of full broadband VLF data, however, leaves significant room for improvement. New systems that can provide high temporal and frequency resolution while being as robust, low-power, and physically small as possible would provide both better data quality as well as lower operational costs in such an extreme location.

## 2.3.3 South Pacific Buoys

The South Pacific Buoys were a research platform designed by Stanford University and deployed in early March 2007. The buoys were related to the High Frequency Active Auroral Research Program, or HAARP, a large HF heater located outside of Chistochina, AK. The buoys themselves were designed to provide reception of HAARP-produced ELF/VLF signals at its geomagnetic conjugate point. The particular research focused on the one-hop phenomena and natural methods of VLF amplification and dispersion [23]. These signals were expected to occur well within

Figure 2.3: Block diagram of a sample AGO receiver

the ELF band, however the system was designed to include full ELF/VLF broadband and narrowband capabilities for added research while at the conjugate point, as well as for deployment of identical electronics systems at other locations, such as Tern Island which shipped prior to buoy deployment.

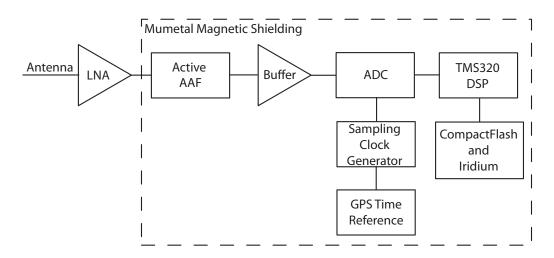

The buoys were limited in antenna size by the radome structure, however still contained two six foot square vertical antennas plus one 5.5 foot circular horizontal antenna, providing measurements of all three axes of magnetic field. The LNA was similar to that of the AWESOME receiver, and an active AAF was also used. Due to physical restrictions of fitting onto the buoy, the main system electronics were virtually co-located with the antenna, being directly below the center of the antenna by only a few feet. To minimize system noise, the main electronics were housed in

mumetal, a magnetic shielding nickel-iron alloy, and significant effort was placed on power system noise shielding and filtering. The custom electronics digitized the VLF radio signals at 16-bit resolution with 100 kHz sample rate, also synchronized with Universal Time by GPS allowing for interferometric studies similar to AWESOME. The processing system consisted of a Texas Instruments TMS320 digital signal processor plus a stack of up to four CompactFlash cards. The processor was capable of continuous time recording at full broadband sampling, as well as near-real-time narrowband demodulation. A block diagram of the buoy electronics is shown in Figure 2.4.

Figure 2.4: Block diagram of the South Pacific Buoy

Although designed to exclusively retrieve its schedule and transmit collected data via Iridium, the buoy electronics can be operated without satellite communications for pre-scheduled recordings and processing, maintaining the data exclusively on the CompactFlash cards. In this mode, the buoys consume approximately 15 Watts for a single system. Although deployed as double-redundant on each buoy, the system

was designed to run only a single system at a time, failing over in the event of a hardware failure. The buoys were able to recharge themselves via solar panels, and were rated for a one-year on-station operational life. These systems were able to function autonomously and in an extreme environment, however without sunlight, as is the case in Antarctica for half of the year, the systems would be unable to recharge. The buoys each shipped with 2,000 pounds of sealed lead acid batteries to ensure operation throughout the low, but still present, sunlight winter months. The large battery bank would not operate at temperatures significantly below freezing, and are extremely heavy making them impractical for Antarctic deployment.

## 2.4 Existing Receiver Limitations

An ELF/VLF receiver system can be characterized by many different performance metrics, including frequency response, minimum detectable signal, sampling rate, sampling resolution, time synchronization, size, weight, average power and peak power. With a firm grasp on signal integrity and sensitivity properties, as demonstrated on the AWESOME and buoy receiver systems, attention can turn to time and frequency resolution, size, weight, and power.

For remote observations, it is critical that the total system volume and mass, including the power source, is as small as possible to reduce deployment costs. Large systems, such as AGO, are only feasible with significant funding and even then are limited in the number of deployment sites. The buoy system is simply too large, when the required batteries for antarctic operation are added, for deployment to most remote sites. The AWESOME system has a reasonable mass, and is able to be hand-carried by two people on an aircraft if necessary, however a battery bank able to supply several hundred watts continuously for a year is extremely large.

Power requirements clearly can drive the total system mass required for remote

deployments. Systems with average power consumption as low as 10 Watts still requires 87,600 Watt hours per year, or a 7,300 Amp hour battery at 12 Volts. More than an order of magnitude drop in power requirements is necessary with current battery technology to maintain a man-portable power supply for a year of operation. Both novel systems presented in the remaining chapters of this paper exceed this order of magnitude requirement while maintaining comparable data quality.

Data quality itself is another parameter where room for optimization exists on embedded platforms. The AGO system trades reduced computation requirements for extremely poor time and frequency resolution of its data; fine structure features of less than one second are not observable, and frequency resolution is limited to hundreds of Hertz or worse. The exception to this is during the short synoptic broadband window, where a 10 kHz of high fidelity data is available. Collecting the full 30 kHz broadband ELF/VLF data continuously, as is done with AWESOME and optionally the buoys, captures all time and frequency information of the studied signals, leaving no information to imagination.

Figure 2.5: Comparison of VLF Receiver Systems

## 2.5 Contributions of New Systems

This work addresses a longstanding problem in the data acquisition world: high performance and long duration sampling in harsh environments with minimal power consumption. Existing systems discussed have advanced the state of the art to allow VLF recordings in extremely remote locations and harsh environments, but still require at least an order of magnitude more power than desired. To develop a system with better power performance by such a large margin, while still maintaining ruggedness, the problem was approached by an architectural solution.

The proposed architectures focus on the sampling control, sampling read back, data storage, and scheduling systems. These systems are complex, and each involved significant amounts of hardware logic. While the system behavior is deterministic, it is sufficiently complex that standard timing and power simulations may not prove the actual, real-world performance of the system as a whole, especially in the extreme environments targeted. Due to the complexity of the solutions presented, and especially the interdependence of the system components on various pieces of disparate ICs, the architectures have been implemented and tested in laboratory and operational conditions, proving, and sometimes exceeding, the predicted improvements from the design stage. The underlying new architecture design represents a significant leap in the state of the art for sampling systems in the target frequency regime, while the straightforward implementation proves not only the performance, but utility of new systems based on the described architecture.

The following chapters describe in detail both a highly refined traditional sampling architecture used to capture synoptic (or optionally continuous) but full-bandwidth broadband data as well as an entirely new sampling architecture for ultra-low power continuous sampling of ELF/VLF data. The Penguin system replaces a traditional microprocessor for the data acquisition system with a highly

customized processor within an FPGA, along with a microcontroller for ultra-low power sleep modes of the system. The VAT system, subsequently described, is a radically new architecture, removing the general purpose CPU from the sampling loop, replacing it with a CPLD containing a highly-tuned sampling and recording controller.

Both new systems provide greater than one order of magnitude power savings, even while operated in continuous sampling modes, extremely small physical footprints, and demonstrated reliable operation in extreme environments. These new capabilities permit experiments in extreme locations that were previously impossible or financially and logistically impractical. The novel ultra-low power architecture developed for VAT is also widely applicable to any continuous sampling system, including acoustic, sonar, and optical devices.

# Chapter 3

# Penguin Micro-VLF Receiver

# 3.1 Background

The Penguin Micro-VLF Receiver is an ELF/VLF receiver system designed for exploration of scientific phenomena which are most readily studied in the polar regions. These phenomena take place in the outer regions of the Earth's magnetosphere, and the resulting VLF waves are often ducted along the magnetic field line back to the Earth's surface. Since the location of the phenomena are in the outer regions of the magnetosphere, or at high "L-Shell", the waves are most easily received at high geomagnetic latitude, requiring the placement of such receiver systems in the extreme environment of the polar regions [49]. The specific phenomena to be studied, such as Auroral Hiss and Chorus, require broadband reception of VLF signals over long, multi-hour, periods. Due to the remoteness of the Antarctic Plateau where the system is deployed, it is imperative that the Penguin system is capable of autonomous operations for at least one year per deployment, while withstanding the extreme environment and lack of external power. Additionally, since deployment operations are extremely expensive with highly restricted logistics, the system must be as lightweight and low volume as possible.

Existing VLF receivers, as outlined in Section 2.3, consume tens of watts of power for broadband VLF reception and physically are rather massive, especially once a one year supply of batteries is added. These systems often include high power CPUs which are always running at full speed, even if idle, while the VLF data is recorded, such as with AWESOME. Some utilize a more power-efficient DSP, such as the buoy or AGO system, however even these more efficient DSPs are power hungry (several watts of power at idle), and during a majority of the sampling process the DSP is also idle. Having high clock rate digital devices running while idle during the time between sampling cycles is clearly not the most efficient use of power, although it is the typical implementation method of current sampling systems.

To combat these problems, the Penguin system utilizes a Field Programable Gate Array (FPGA), which is effectively a sea of programmable logic, to implement a customized CPU that minimally meets the sampling system requirement to conserve as much power as possible. By stripping out any extra peripherals and core CPU items which are not necessary, such as MMUs or advanced computational instructions, there is less logic to be clocked or to leak power and thus less power consumed overall. Also, by reducing the CPU clock speed to the minimum frequency for the device to keep up with the required sampling, the dynamic power is further reduced. These architectural changes remove the Penguin system from being simply the next incarnation of a standard architecture, implemented on the newest silicon, to a significantly more refined processing flow, providing performance enhancements over traditional architectures regardless of the underlying hardware. The overall Penguin architecture represents a highly-optimized digital sampling system for VLF data acquisition that exceeds the power performance of any other known comparable VLF system by more than an order of magnitude. The architectural design process hints at the anticipated performance improvements, while the implementation and deployment of this new architecture prove the end performance, operational success,

and utility of the new system design.

## 3.2 Derivation of Requirements

The first, and arguably most important, step of scientific instrument design is to define the requirements of the device as completely as possible. We will take a ground-up approach and start with the scientific constrains and requirements, followed by derived requirements from the scientific objectives, and lastly will consider logistical and operational concerns.

For the study of high L-Shell phenomena such as Auroral Hiss and natural Chorus emissions, we can directly determine the VLF bandwidth requirements and start to determine the minimal system dynamic range. Studies have indicated that Chorus is typically band limited to under 2.5 kHz [11]. Hiss, on the other hand, is present over a much larger band which includes the entirety of the 30 kHz VLF band [34, 39]. Thus, due to the larger frequency constraints of Hiss, Penguin must sample the entire 30 kHz ELF/VLF band. For Nyquist sampling, the sample rate or  $F_s$  must be at least 60 kHz [35]. However, this assumes that the anti-aliasing filter has perfect frequency response with infinite cutoff for out of band signals, which is not at all realizable. On a practical note, to achieve 50dB of stopband rejection an additional 10%, or 6 kHz, of sample rate is sufficient for an active-element anti-aliasing filter. These active filters, however, can consume significant amounts of power (hundreds of milliwatts), and due to the ultra-low power requirement for Penguin are less than ideal. To combat this waste of power, Penguin uses a passive element anti-aliasing filter which consumes approximately 20 mW of power. This passive filter, however, requires nearly 20 kHz of roll-off to reach comparable stopband performance. Thus, the required sample rate is much closer to 100 kHz. This trade-off selection is valid only if the required increase in power due to the higher sampling frequency is less

than the additional power that an active filter would required, and is proven to be true later in this chapter. Additionally, since it is often useful to determine the physical origination location of a signal, two orthogonal receiver channels are necessary, which follows the classical antenna type for an ELF/VLF ground-based receiver.

The dynamic range requirements of the Penguin system are not as clear-cut as the frequency requirements. Dynamic range encompasses information about the background noise level of the environment and receiver system where it is installed as well as the signal strengths of both the weakest and strongest signals present that are desired to be studied and thus must be recorded in an undistorted fashion. Existing ELF/VLF receiver systems on the Antarctic Plateau to study the same phenomena, such as the AGO systems, have a 12-bit ADC at the front end without any automatic gain control, thus limiting the dynamic range to at most 74 dB. Data from these systems, however, typically exhibit closer to 50 dB of dynamic range which has been sufficient for all scientific studies thus far. As such, the Penguin system is designed to have a dynamic range of at least 50 dB end to end, with a desire to increase this range as much as practical.

Along with frequency and amplitude requirements on the data come time. Time is important for both how much data must be collected (i.e. data volume) as well as how accurately the time stamp of the data must be. First it is necessary to determine how much data must be collected to still be useful. Chorus and Hiss are long term phenomena which develop over hours, however it is not necessarily practical to record all of this data due to power and storage limitations. Minimizing the volume of data recorded eases meeting the longevity requirements of the system. In consultation with the data end users, it is determined that a 2-second snapshot once every fifteen minutes would be ample to study the ambient ELF/VLF environment. Combined with the larger bandwidth of Penguin and possibly higher dynamic range, Penguin

will provide better broadband data than is currently available from the large and expensive AGO systems. This snapshot mode also greatly reduces data compared to continuous recording.

With a determination of the volume of data complete, the absolute timing accuracy of the system must be specified. For the studies being conducted with Penguin, it is ideal for at least some of the data from each snapshot collected by each of multiple Penguin units across the Antarctic Continent to overlap. More formally, the frequency departure of the timing system for each Penguin receiver must be small enough to ensure that no system drifts more than one second per time synchronization period. With the readily available nature of simple crystal oscillators with normalized frequency departures of less than  $10^{-11}$ , time synchronization can be as infrequent as once per day to easily maintain this requirement [2]. Since time synchronization is a potentially costly operation in terms of power, limiting this synchronization frequency is another method of reducing overall power consumption.

Now that bandwidth, dynamic range, and duration have been established, the amount of storage space can be calculated. To maximize the dynamic range and ensure that the sampling and digital systems are not the limiting factor, a 16-bit analog-to-digital converter (ADC) is selected for Penguin. This results in one 16-bit word (or 2 bytes) per sample per channel. Taking this data from two independent channels with  $F_s = 100$  kHz results in 400,000 bytes of data per second. With a recording schedule of two seconds every 15 minutes, 76.8 MBytes are sampled per day or just over 28 GBytes per year. In addition to this 28 GBytes of ELF/VLF data, several hundred MBytes should be available for system logs and timekeeping information, resulting in a storage requirement of approximately 30 GBytes per year which is feasible with currently available COTS flash storage mediums.

Power and physical volume should be minimized as low as practically possible. Existing receiver systems require hundreds if not thousands of pounds of batteries or fuel to operate per year, with the AGO systems requiring an entire small building to operate. Penguin must be transportable for extremely remote deployment, with weight limits typically in the hundreds of pounds for cargo. Less power and less weight are obviously ideal, and should be the top priority and consideration in design tradeoffs after the basic scientific requirements previously outlined are met.

Lastly, the Penguin system must be able to operate in one of the harshest environments on the planet. Temperatures in Antarctica are extraordinarily cold ( $\leq -50^{\circ}$ C), with 6 months of continual darkness each year. The snow itself can be used as an insulator, maintaining a relatively constant -55° C throughout the year even as temperatures plunge below -70° C in the winter [58]. Components selected for use must be able to either operate in these extreme temperatures, or be sufficiently insulated from the outside environment, possibly with the addition of heaters, to function properly. While many integrated circuits are rated to this temperature by binning of production chips, it is important to note at that many battery technologies freeze and cease to function at significantly warmer temperatures than are expected with Penguin.

## 3.3 System Architecture

## 3.3.1 Background

While Penguin is designed to take as much as possible from legacy ELF/VLF receiver systems, the key to Penguin's success is to modernize them to the most recently available technologies, and reduce the system power while maximally increasing the system performance. By utilizing legacy system architectures, risk to the Penguin program is minimized as compared with taking a radical approach using an unproven and/or novel architecture. Additionally, the lessons learned over

years of systems design can be incorporated to end with a polished finished product. Lastly, due to advances in semiconductor, battery, and circuit technologies, extremely careful design of the new Penguin system can greatly reduce power consumption as compared to any other known system, while maintaing as good, if not better quality of data. Penguin as a system serves to illustrate the best possible performance from these legacy high-level system designs. The VAT system, a radical new architecture described in chapter 4, uses Penguin as the baseline best possible traditional system to demonstrate the extreme performance possible by changing the fundamental architecture of ELF/VLF receiver systems.

The traditional architecture adopted by Penguin is shown in Figure 2.1, where the "Signal Processor" block is the main system CPU. Penguin, however, replaces this commodity CPU with an FPGA and customized CPU to critically meet the system performance requirement without having additional wasted capabilities that are unused but still consume power. For the innovative design trade studies and decisions necessary to accomplish order of magnitude better power consumption over existing systems an in-depth look of each sampling subsystem is required.

## 3.3.2 Analog Front End

The analog front end used in the Penguin system is the results of a separate inhouse development effort of a magnetic field low noise amplifier application specific integrated circuit. The second fabricated version of this chip, designed by Stanford VLF Graduate Student Sarah Harriman, is used in the deployed Penguin system. The specific LNA ASICs used in the system provide greater than 60 dB of spurious free dynamic range (SFDR) across the entire ELF/VLF band. The implementation details of the LNA itself are outside the scope of this document as they are not the author's work. The use of the LNA in the system, however, is critical for determining the minimum requirements for the remainder of the system.

As indicated in Section 3.2, a passive anti-aliasing filter is required to reduce the system power consumption. A seventh order Cauer elliptical filter is selected to provide approximately 80 dB of stopband rejection for 100 kHz sample rates, with the maximum unaliased frequency of 30 kHz [56]. The filter is based around a chain of capacitors and inductors to form the actual filter, plus an Analog Devices AD8606 instrumentation-grade operational amplifier to counteract the filter losses as well as add system gain to match the front end with the analog-to-digital converter.

The implemented filter utilized custom wound inductors with an extremely high Q to provide the sharpest roll-off possible. The custom inductors contain a pot-core with an internal gap to reduce the temperature dependence of the impedance. Inhouse testing of commercial, non-gapped cores resulted in 10 dB of attenuation at the maximum unaliased frequency and 30 dB less stopband rejection when cooled to -55° C, as compared to the identical circuit with custom gapped pot-core inductors.

A separate AAF is required for each of the two VLF channels. Both AAFs are designed to fit on a single card which directly plugs into the digital printed circuit board, which contains the sampling, processing, and data storage systems. By having the AAF as a removable module, different filter topologies, bandwidths, roll-offs, and gains may be inserted into the Penguin system without significant modifications for easy adaptability to future scientific needs or differing LNAs. This modular approach has been extremely beneficial in the AGO and AWESOME systems.

Penguin does allow, however, for a significant separation between the low noise amplifier and the remainder of the electronics, most importantly the digital system. This separation is most common with AWESOME system deployments, where the AAF and receiver PC are located indoors near power lines, while the antenna, LNA, and line driving circuitry are located hundreds or thousands of meters away from such interference sources. Penguin, due to its extremely low power consumption during operations and careful system design, has minimal radiated emissions and

thus does not require large separations for interference-free data. The separation capability, however, is maintained in Penguin for these legacy reasons.

#### 3.3.3 Sampling System

The sampling system of Penguin directly interfaces between the main processing unit and the analog signals provided by the front end AAF described above. In the traditional architecture used in Penguin, the analog-to-digital converter is the only component that is exclusively part of the sampling system; the main CPU is implied as controlling the ADC as required to perform sampling operations. The principal requirements on the ADC itself include input signal type and voltage range, supported sampling rates, sampling resolution, performance (SFDR/SINAD/ENOB), supply voltages, digital interface type, and power consumption.

As the most basic requirement, the ADC must be able to properly interface electrically with the front end. Penguin utilizes a differential signaling type out of the LNA to minimize induced signals on the wires [44]. Single-ended signaling provides no common mode rejection, and is ill-suited for long runs of sensitive signals, thus making differential signaling especially important for the potentially long link between the LNA and AAF/sampling system. The AAF itself is intrinsically single-ended, but immediately converts back to differential to again maintain good noise immunity between the AAF and the actual ADC inputs. Thus, for maximum signal integrity, a differential input ADC must be used.

The performance of the ADC, namely the Spurious Free Dynamic Range (SFDR), Signal plus Noise And Distortion (SINAD), and Effective Number of Bits (ENOB) must be selected to at least meet, if not exceed, the similar specifications of the entire front end section plus the anticipated signals. The LNA, as tested in a laboratory setting, provides not less than 60 dB of SFDR, while the AAF provides at least 80 dB of stopband rejection. Thus, the ADC must have at least 80 dB of SFDR to

avoid being a limiting factor in system performance. This results in a requirement of at least 13 ENOB for the currently used LNA and AAF.

The signal to be sampled is not only filtered but also amplified within the AAF section to better match the voltage rails of the ADC. The voltage rails of the AAF are set to 3.3 V to accept the maximal 2.5 V signal from the LNA with minimal distortion. Amplifying the signal to levels too close to the voltage rails of the operational amplifier can result in signal distortion; the devices are most linear for small signal levels. Thus, we should expect the signals leaving the AAF to also be limited to approximately 2.5 V maximum. On the ADC side, however, maximizing the rail span of the signal is important for utilizing the full dynamic range of the converter. This is the typical tug-of-war between the analog designer's desire to keep the signal levels low to maximize linearity of the components in use versus the digital/ADC designer's desire to maximize the span of the signals compared to the ADC rails to maintain the highest dynamic range. As a compromise in Penguin, a 3.3 V supply is used in the AAF gain stages while keeping the maximal signal amplitude below 2.5 V. The ADC, however, is selected to have a 2.5 V rail span to match the analog signal, while having a 3.3 V digital I/O level to mesh with the selected processor without the need for level converters. 3.3 V is selected for the main processor to also match the voltage requirements of the selected nonvolatile storage medium discussed in Section 3.3.6.

Several digital interfaces are available to connect the ADC to the main processor, with parallel versus serial being the first branching point in the decision. Parallel will provide a separate signal path for each bit of the sampled value, plus control lines. While this allows the data to be read out from the ADC in a single CPU clock cycle, it does require a significant number of I/O lines and signals to be routed on the board. Serial interfaces, on the other hand, allow for typically 2-4 I/O lines to be used for the same data, however additional complexity is necessary inside of the

CPU to process the bit stream. Many CPUs include serial interfaces as dedicated peripherals, so this additional processing requirement is minimal. Thus, a serial interface will maintain minimal complexity in the physical system with no other impact on system performance with this architecture.

As discussed in Section 3.2, the ADC samples at 100 kHz, resulting in 200 kBytes per second or 1.6 MBits per second of data output assuming a 16-bit ADC. At face value one might interpret this to indicate that the digital interface must be able to transfer 1.6 Mbps, however this is incorrect. Most ADCs require that the readback of a sample be completed prior to the commencement of the next sample and hold. The actual analog-to-digital conversion is also not an instant process, even on a Flash ADC, and thus less than the entire sample period is available for readback, with often only about half of the period free. This timing limitation varies greatly by each specific ADC, but must be accounted for when designing the digital interface. Assuming that 50% of the sampling period is available for readback, the Penguin digital interface must operate at least 3.2 Mbps. Serial Peripheral Interface (SPI) is the most common serial interface used by ADCs with multi-megabit per second bandwidths, and thus is the ideal candidate for use in Penguin.

Combining all of the requirements of this section along with a survey of currently available COTS ADCs, the Analog Devices AD7687 is selected [20]. This ADC provides 96 dB of dynamic range, and over 93 dB of SINAD at the desired frequency and voltage operating conditions present in Penguin. The differential input allows for a fully differential analog signal path depending on the specific AAF used in the application, while the SPI digital interface allows for a minimum pin-count interface between the host processor and ADC. Lastly, the AD7687 is selected for its extremely low power consumption compared to other available devices, which is paramount for long-term autonomous operation.

#### 3.3.4 Time Keeping and Synchronization

As driven by the scientific data requirements outlined in Section 3.2, Penguin must internally know the time with better than one second accuracy at any given instant. This absolute timing requirement translates to a normalized frequency departure, Y(t), of one part in 86,400 or approximately  $10^{-5}$  [3]. This Y(t) requirement is extremely easy to obtain with modern crystal oscillators, which typically provide Y(t) from  $10^{-8}$  to  $10^{-9}$ . Given  $Y(t) = 10^{-8}$ , one can expect approximately an 860  $\mu$ s departure per day, which is significantly longer than a single sampling period at 100 kHz. While Penguin is not required to have subsample absolute timing resolution, it is important to understand that such resolution is possible with a crystal oscillator time base given that it is resynchronized at least every 16 minutes, given the assumed  $Y(t) = 10^{-8}$ .

To minimize power consumption while still maintaing rather accurate time information, Penguin is designed to resynchronize its internal oscillator with a time standard once per day, yielding an expected normalized frequency departure of 860  $\mu$ s. This design allows for data from multiple Penguin sites to be compared with general ease, however still without interferometry capabilities which are discussed later in this section. The time standard most available to Penguin in such remote locations is GPS, which provides 10 ns level time accuracy globally utilizing relatively small and low power receivers [36]. The selected GPS receiver is an i-Lotus (formerly Motorola) M12M timing receiver [28]. This receiver provides a 1 pulse per second (PPS) output that is synchronized to UTC within 20 ns. In addition, this timing output can be delayed by an arbitrary, programable amount to compensate for cable and output propagation delays.

The main timekeeping system consists of a high-precision quartz crystal oscillator combined with a discrete logic counter and two discrete logic dividers. The main crystal, clocked at 2 MHz, is divided down to the sampling clock frequency of 100

kHz. This 100 kHz signal is then continuously counted in a discrete, low power logic, 40-bit counter. This counter allows for more than 100 days of timekeeping; however, note that a 32-bit counter, which is the next smallest available counter constructed from COTS 8-bit parts, would be unable to keep track of time for even a single day. In addition to the 100 kHz counter, the same signal is also divided down to create a 1 PPS signal, used to determine the instant that the system should begin sampling on the integer second boundary of wall clock time. Lastly, the exact UTC date and time when the counters and dividers were last re-synchronized and reset is maintained in non-volatile memory in the system control microcontroller. In total, the system thus tracks the last time the internal clock was reset as well as an internal stopwatch of the estimated time elapsed since then. Combining these two pieces of information allows the system to know the current UTC time to the accuracy of the internal crystal oscillator. The system also knows how much time has elapsed since the last resynchronization and thus can schedule time resynchronizations as necessary. The principle hardware constituents of the timekeeping and resynchronization system are shown in Figure 3.1.

Figure 3.1: Penguin Time Keeping System

The resynchronization process occurs due to either the system powering on from a previously powerless state or when the time since last update is greater than 24 hours. In the first case, during bootstrap the system control microcontroller clears the last synchronization time from its internal memory, forcing a time update when the main system processor comes online. In the later case, the main system processor directly determines from a read of the timekeeping counter that at least 24 hours has elapsed. In either case, the actual synchronization process is the same. First, the main processor must be running in addition to the system control microcontroller (see Section 3.3.7 for details). Next, the main system processor instructs the system control processor to power on the GPS receiver. This functionality is not directly handled by the main system processor to avoid accidentally powering on the GPS system due to glitches on the main system processor's I/O lines during power-up. If the GPS power is directly controlled by the main system processor, as in earlier revisions of the Penguin system, the internal 1 PPS signal would be corrupted on a random basis.

With the GPS powered up, the main system processor initializes the GPS receiver for proper settings, such as elevation blanking, UTC time mode, and the requisite 1 PPS delay time. The GPS is then polled once per second until both GPS signal lock is achieved as well as the number of leap seconds is updated. The leap seconds count is required to calculate true UTC from the GPS time, and is only received once per GPS navigation message, which may take up to 12.5 minutes to receive after lock on the first GPS satellite is acquired [17]. Once locked, the 1 PPS counter is automatically resynchronized to the edge of the 1 PPS signal from the GPS. The 100 kHz counter is read back on one of these 1 PPS edges, as well as the exact true UTC time for the GPS receiver. These two pieces of information are recorded to a log file and are used to back out the drift of the Penguin oscillator for postprocessing of the data after the system is recovered from the field. On the next 1 PPS edge, the 100 kHz counter is cleared and the 100 kHz generator is reset, and the UTC time of the reset is stored in the system control microcontroller's internal memory. This process assures that both the 100 kHz signal as well as the internal 1 PPS signal are within one 2 MHz period (500 nS) of true UTC.

The 500 ns accuracy limit is the direct result of using a 2 MHz internal crystal. By replacing the crystal with a VCO or other device with adjustable phase, this 500 nS limit can be removed, however at a significant power penalty. This limit also is quickly overshadowed by the frequency departure of the crystal itself and thus is not a prime candidate for optimizing system time performance. The system should, however, be calibrated at the anticipated operating temperature to remove any UTC offsets. Since the clear signal to the counters and dividers has a non-zero propagation time, especially when the delay of the GPS 1 PPS edge detector is added, the system clock has an intrinsic offset from actual UTC. This offset, however, is directly due to the components involved and board layout, and thus can be calibrated for when each board is manufactured. The calibration process consists of running the system and allowing it to resynchronize with GPS without any propagation delay factor programmed into the GPS receiver. The output 1 PPS edge from the Penguin system clock should then be observed on an oscilloscope with a scan rate of at least 100 nS per division, if not faster. On another channel of the oscilloscope, a reference 1 PPS signal, possibly directly from the onboard GPS receiver, should be simultaneously viewed. The offset between these two signals is then measured and programmed into the Penguin system as the desired GPS cable delay factor. This process can be iterated if necessary to minimize the timing difference.

If a higher level of timing precision is necessary, the GPS resynchronization period can be decreased, or for maximal precision the GPS receiver can be used to constantly discipline a 100 kHz clock source. There are many methods possible for constant GPS disciplining. The method used in both the AWESOME receivers as well as the buoys utilized a high frequency Voltage Controlled Oscillator (VCO) running at 40 MHz, which was directly disciplined and divided down to the required 100 kHz clock. By fine tuning the frequency of this HF oscillator, and allowing for the divide down factor to be digitally controllable, the accuracy of the output clock